Functions | |

| void | snor_device_init (SNORDriver *devp) |

| flash_error_t | snor_device_read (SNORDriver *devp, flash_offset_t offset, size_t n, uint8_t *rp) |

| flash_error_t | snor_device_program (SNORDriver *devp, flash_offset_t offset, size_t n, const uint8_t *pp) |

| flash_error_t | snor_device_start_erase_all (SNORDriver *devp) |

| flash_error_t | snor_device_start_erase_sector (SNORDriver *devp, flash_sector_t sector) |

| flash_error_t | snor_device_verify_erase (SNORDriver *devp, flash_sector_t sector) |

| flash_error_t | snor_device_query_erase (SNORDriver *devp, uint32_t *msec) |

| flash_error_t | snor_device_read_sfdp (SNORDriver *devp, flash_offset_t offset, size_t n, uint8_t *rp) |

| void | snor_activate_xip (SNORDriver *devp) |

| void | snor_reset_xip (SNORDriver *devp) |

Variables | |

| flash_descriptor_t | snor_descriptor |

| Flash descriptor. | |

| const wspi_command_t | snor_memmap_read |

| Fast read command for memory mapped mode. | |

Detailed Description

Function Documentation

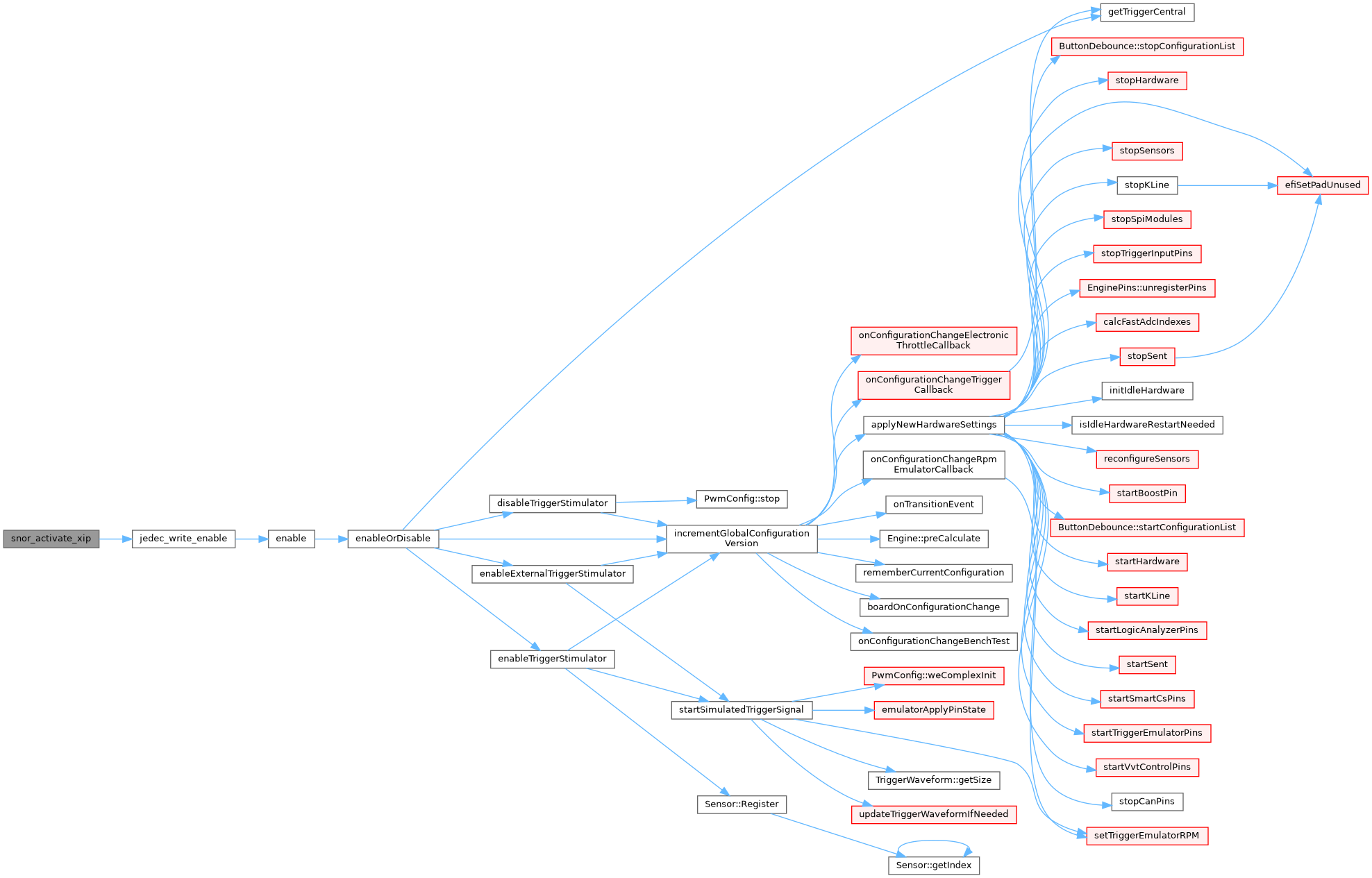

◆ snor_activate_xip()

| void snor_activate_xip | ( | SNORDriver * | devp | ) |

Definition at line 581 of file hal_flash_device.c.

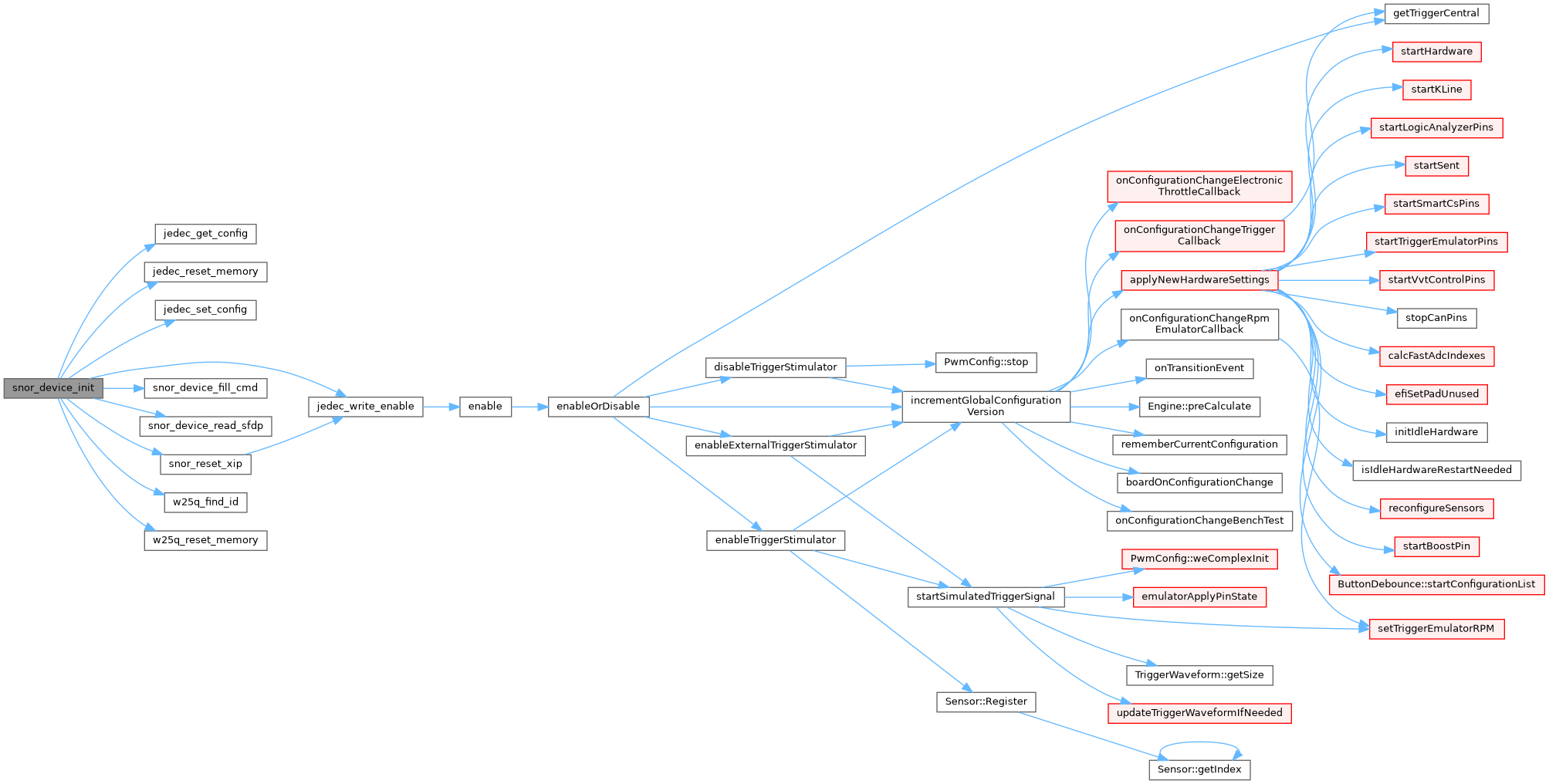

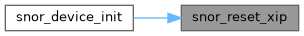

◆ snor_device_init()

| void snor_device_init | ( | SNORDriver * | devp | ) |

Definition at line 264 of file hal_flash_device.c.

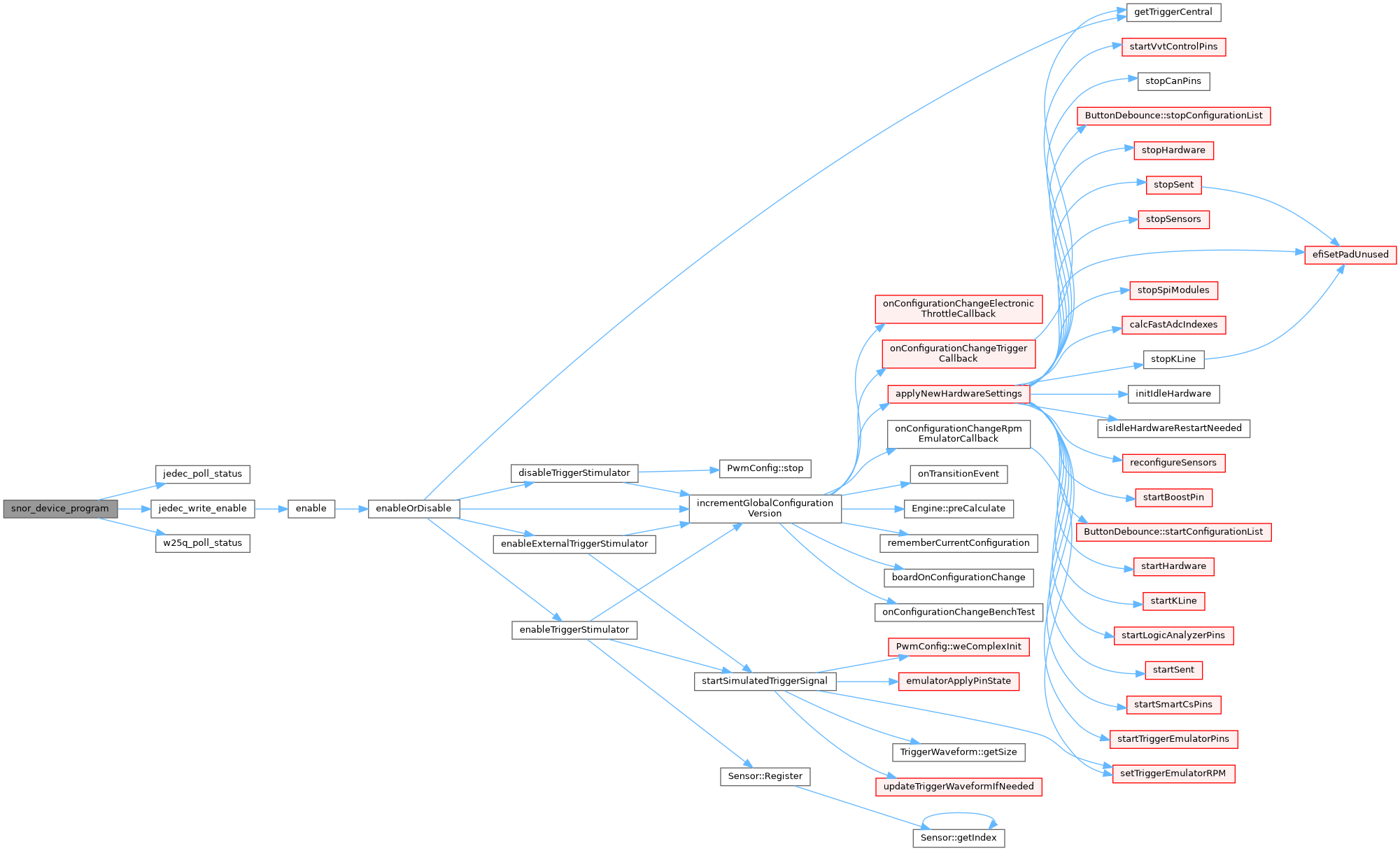

◆ snor_device_program()

| flash_error_t snor_device_program | ( | SNORDriver * | devp, |

| flash_offset_t | offset, | ||

| size_t | n, | ||

| const uint8_t * | pp | ||

| ) |

Definition at line 428 of file hal_flash_device.c.

◆ snor_device_query_erase()

| flash_error_t snor_device_query_erase | ( | SNORDriver * | devp, |

| uint32_t * | msec | ||

| ) |

Definition at line 524 of file hal_flash_device.c.

◆ snor_device_read()

| flash_error_t snor_device_read | ( | SNORDriver * | devp, |

| flash_offset_t | offset, | ||

| size_t | n, | ||

| uint8_t * | rp | ||

| ) |

Definition at line 409 of file hal_flash_device.c.

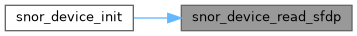

◆ snor_device_read_sfdp()

| flash_error_t snor_device_read_sfdp | ( | SNORDriver * | devp, |

| flash_offset_t | offset, | ||

| size_t | n, | ||

| uint8_t * | rp | ||

| ) |

Definition at line 546 of file hal_flash_device.c.

Referenced by snor_device_init().

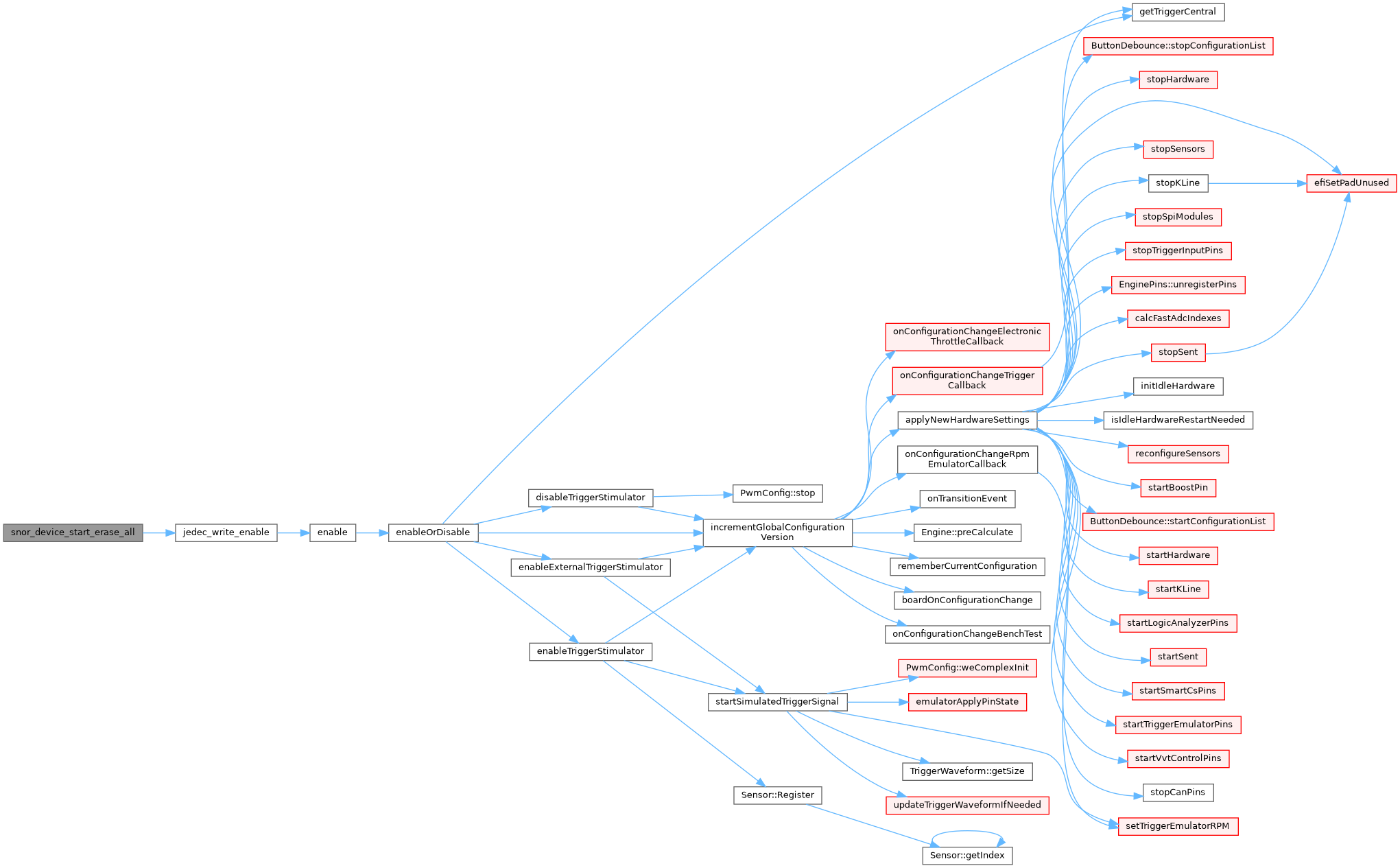

◆ snor_device_start_erase_all()

| flash_error_t snor_device_start_erase_all | ( | SNORDriver * | devp | ) |

Definition at line 464 of file hal_flash_device.c.

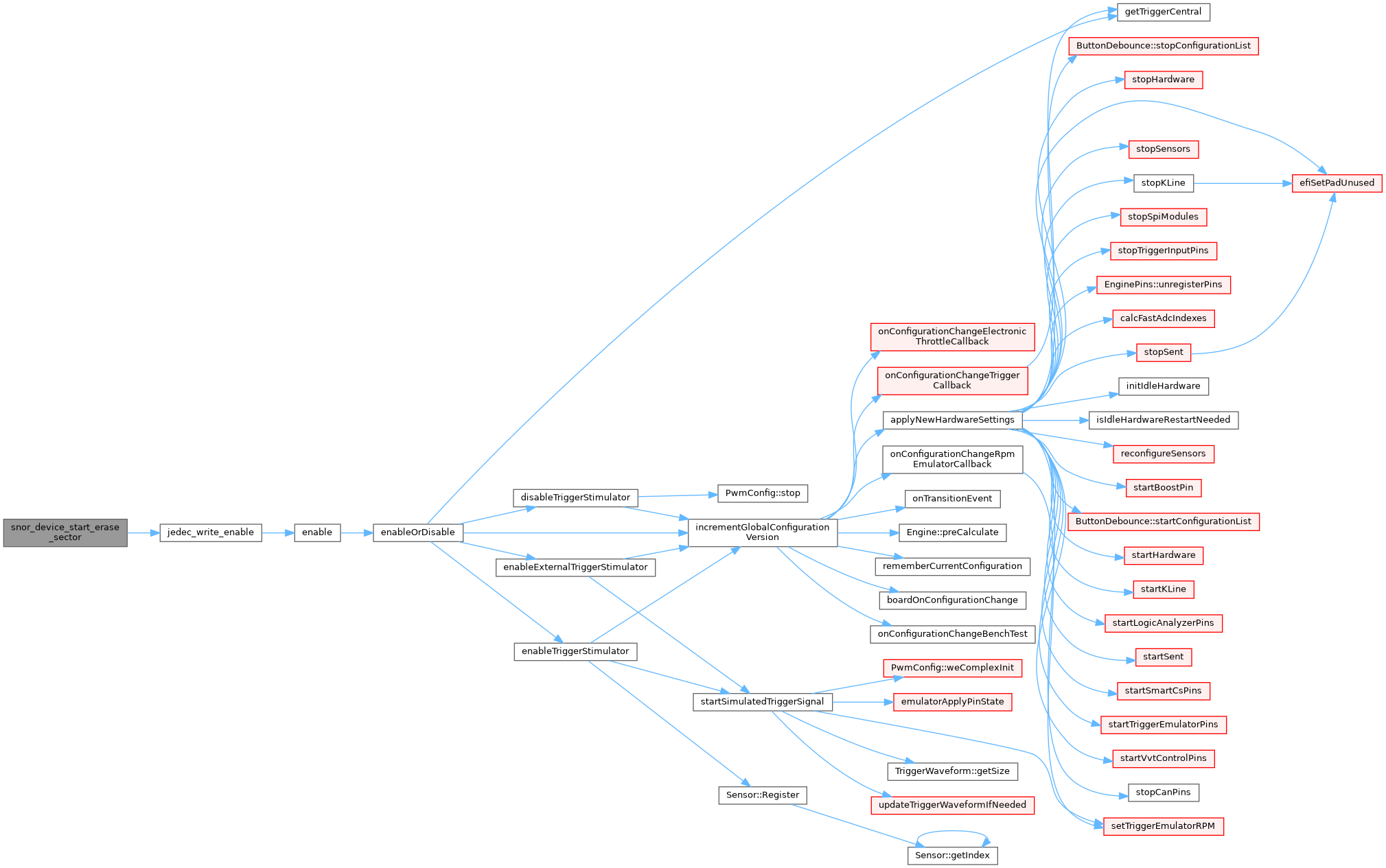

◆ snor_device_start_erase_sector()

| flash_error_t snor_device_start_erase_sector | ( | SNORDriver * | devp, |

| flash_sector_t | sector | ||

| ) |

Definition at line 475 of file hal_flash_device.c.

◆ snor_device_verify_erase()

| flash_error_t snor_device_verify_erase | ( | SNORDriver * | devp, |

| flash_sector_t | sector | ||

| ) |

Definition at line 489 of file hal_flash_device.c.

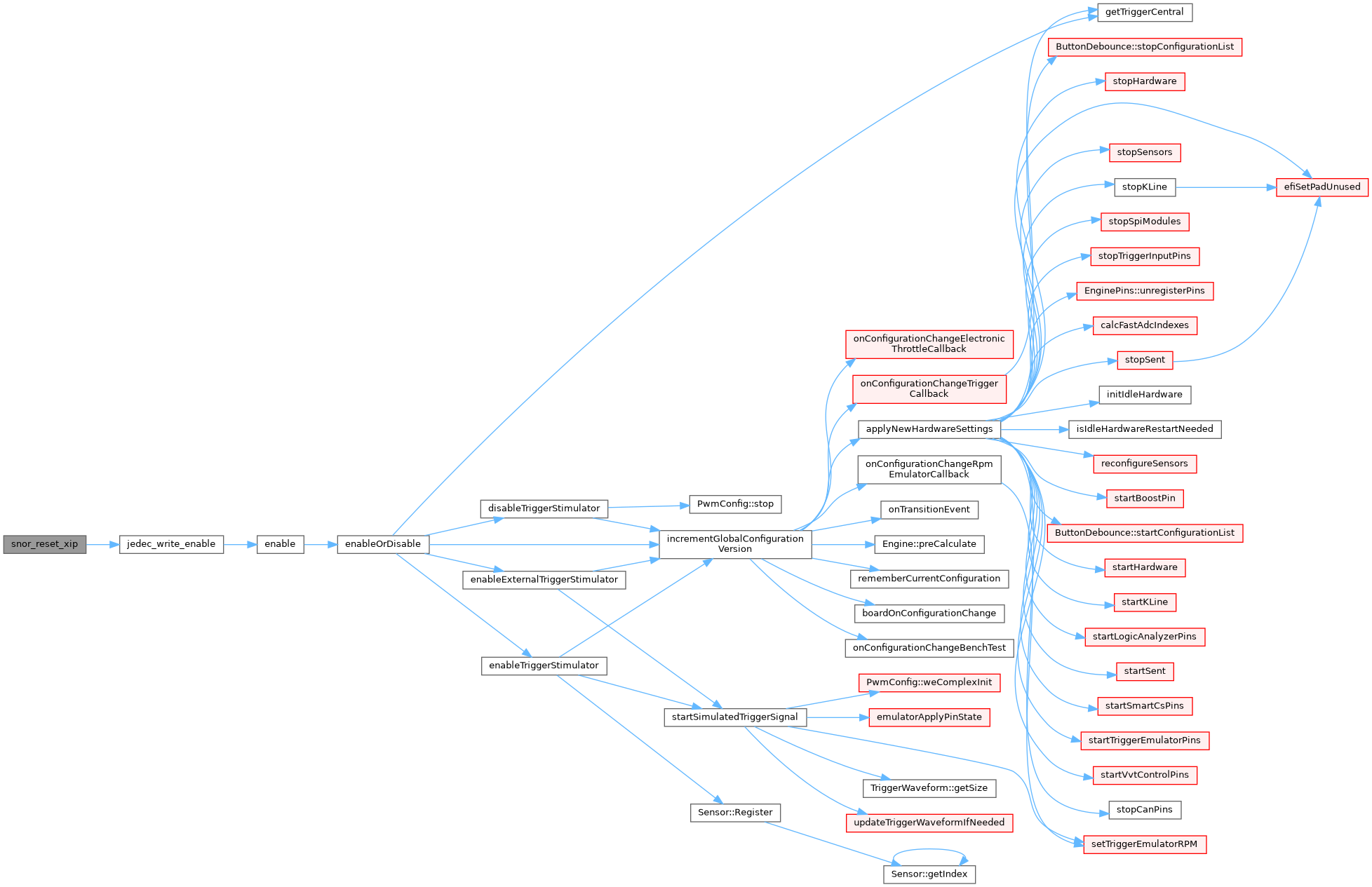

◆ snor_reset_xip()

| void snor_reset_xip | ( | SNORDriver * | devp | ) |

Definition at line 595 of file hal_flash_device.c.

Referenced by snor_device_init().

Variable Documentation

◆ snor_descriptor

|

extern |

Flash descriptor.

Flash descriptor.

Definition at line 39 of file hal_flash_device.c.

Referenced by snor_device_init(), snor_device_program(), snor_device_start_erase_sector(), and snor_device_verify_erase().

◆ snor_memmap_read

|

extern |

Fast read command for memory mapped mode.

Definition at line 56 of file hal_flash_device.c.