Files | |

| file | fsl_clock.h |

Data Structures | |

| struct | _scg_sys_clk_config |

| SCG system clock configuration. More... | |

| struct | _scg_sosc_config |

| SCG system OSC configuration. More... | |

| struct | _scg_sirc_config |

| SCG slow IRC clock configuration. More... | |

| struct | _scg_firc_trim_config |

| SCG fast IRC clock trim configuration. More... | |

| struct | _scg_firc_config_t |

| SCG fast IRC clock configuration. More... | |

| struct | _scg_spll_config |

| SCG system PLL configuration. More... | |

Driver version | |

| enum | _clock_name { kCLOCK_CoreSysClk , kCLOCK_BusClk , kCLOCK_FlexBusClk , kCLOCK_FlashClk , kCLOCK_ScgSysOscClk , kCLOCK_ScgSircClk , kCLOCK_ScgFircClk , kCLOCK_ScgSysPllClk , kCLOCK_ScgSysOscAsyncDiv1Clk , kCLOCK_ScgSysOscAsyncDiv2Clk , kCLOCK_ScgSircAsyncDiv1Clk , kCLOCK_ScgSircAsyncDiv2Clk , kCLOCK_ScgFircAsyncDiv1Clk , kCLOCK_ScgFircAsyncDiv2Clk , kCLOCK_ScgSysPllAsyncDiv1Clk , kCLOCK_ScgSysPllAsyncDiv2Clk , kCLOCK_LpoClk , kCLOCK_Osc32kClk , kCLOCK_ErClk } |

| Clock name used to get clock frequency. More... | |

| enum | _clock_ip_src { kCLOCK_IpSrcNoneOrExt = 0U , kCLOCK_IpSrcSysOscAsync = 1U , kCLOCK_IpSrcSircAsync = 2U , kCLOCK_IpSrcFircAsync = 3U , kCLOCK_IpSrcSysPllAsync = 6U } |

| Clock source for peripherals that support various clock selections. More... | |

| enum | _clock_ip_name { kCLOCK_IpInvalid = 0U , kCLOCK_Dma0 = 0x40065020U , kCLOCK_Sysmpu0 = 0x40065034U , kCLOCK_Flash0 = 0x40065080U , kCLOCK_Dmamux0 = 0x40065084U , kCLOCK_Flexcan0 = 0x40065090U , kCLOCK_Flexcan1 = 0x40065094U , kCLOCK_Ftm3 = 0x40065098U , kCLOCK_Adc1 = 0x4006509CU , kCLOCK_Lpspi0 = 0x400650B0U , kCLOCK_Lpspi1 = 0x400650B4U , kCLOCK_Pdb1 = 0x400650C4U , kCLOCK_Crc0 = 0x400650C8U , kCLOCK_Pdb2 = 0x400650CCU , kCLOCK_Pdb0 = 0x400650D8U , kCLOCK_Lpit0 = 0x400650DCU , kCLOCK_Ftm0 = 0x400650E0U , kCLOCK_Ftm1 = 0x400650E4U , kCLOCK_Ftm2 = 0x400650E8U , kCLOCK_Adc0 = 0x400650ECU , kCLOCK_Adc2 = 0x400650F0U , kCLOCK_Rtc0 = 0x400650F4U , kCLOCK_Dac0 = 0x400650FCU , kCLOCK_Lptmr0 = 0x40065100U , kCLOCK_PortA = 0x40065124U , kCLOCK_PortB = 0x40065128U , kCLOCK_PortC = 0x4006512CU , kCLOCK_PortD = 0x40065130U , kCLOCK_PortE = 0x40065134U , kCLOCK_Pwt0 = 0x40065158U , kCLOCK_Flexio0 = 0x40065168U , kCLOCK_RtcOsc0 = 0x40065180U , kCLOCK_Ewm0 = 0x40065184U , kCLOCK_Lpi2c0 = 0x40065198U , kCLOCK_Lpi2c1 = 0x4006519CU , kCLOCK_Lpuart0 = 0x400651A8U , kCLOCK_Lpuart1 = 0x400651ACU , kCLOCK_Lpuart2 = 0x400651B0U , kCLOCK_Cmp0 = 0x400651CCU , kCLOCK_Cmp1 = 0x400651D0U , kCLOCK_Cmp2 = 0x400651D4U } |

| Peripheral clock name difinition used for clock gate, clock source and clock divider setting. It is defined as the corresponding register address. More... | |

| enum | _osc32_mode { kOSC32_Bypass = OSC32_CR_ROSCEN_MASK , kOSC32_Crystal = OSC32_CR_ROSCEN_MASK | OSC32_CR_ROSCEREFS_MASK , kOSC32_CrystalEnableInStop } |

| OSC32 work mode. More... | |

| enum | _scg_status { kStatus_SCG_Busy = MAKE_STATUS(kStatusGroup_SCG, 1) , kStatus_SCG_InvalidSrc = MAKE_STATUS(kStatusGroup_SCG, 2) } |

| SCG status return codes. More... | |

| enum | _scg_sys_clk { kSCG_SysClkSlow , kSCG_SysClkBus , kSCG_SysClkCore } |

| SCG system clock type. More... | |

| enum | _scg_sys_clk_src { kSCG_SysClkSrcSysOsc = 1U , kSCG_SysClkSrcSirc = 2U , kSCG_SysClkSrcFirc = 3U , kSCG_SysClkSrcSysPll = 6U } |

| SCG system clock source. More... | |

| enum | _scg_sys_clk_div { kSCG_SysClkDivBy1 = 0U , kSCG_SysClkDivBy2 = 1U , kSCG_SysClkDivBy3 = 2U , kSCG_SysClkDivBy4 = 3U , kSCG_SysClkDivBy5 = 4U , kSCG_SysClkDivBy6 = 5U , kSCG_SysClkDivBy7 = 6U , kSCG_SysClkDivBy8 = 7U , kSCG_SysClkDivBy9 = 8U , kSCG_SysClkDivBy10 = 9U , kSCG_SysClkDivBy11 = 10U , kSCG_SysClkDivBy12 = 11U , kSCG_SysClkDivBy13 = 12U , kSCG_SysClkDivBy14 = 13U , kSCG_SysClkDivBy15 = 14U , kSCG_SysClkDivBy16 = 15U } |

| SCG system clock divider value. More... | |

| enum | _clock_clkout_src { kClockClkoutSelScgSlow = 0U , kClockClkoutSelSysOsc = 1U , kClockClkoutSelSirc = 2U , kClockClkoutSelFirc = 3U , kClockClkoutSelSysPll = 6U } |

| SCG clock out configuration (CLKOUTSEL). More... | |

| enum | _scg_async_clk { kSCG_AsyncDiv1Clk , kSCG_AsyncDiv2Clk } |

| SCG asynchronous clock type. More... | |

| enum | scg_async_clk_div { kSCG_AsyncClkDisable = 0U , kSCG_AsyncClkDivBy1 = 1U , kSCG_AsyncClkDivBy2 = 2U , kSCG_AsyncClkDivBy4 = 3U , kSCG_AsyncClkDivBy8 = 4U , kSCG_AsyncClkDivBy16 = 5U , kSCG_AsyncClkDivBy32 = 6U , kSCG_AsyncClkDivBy64 = 7U } |

| SCG asynchronous clock divider value. More... | |

| enum | _scg_sosc_monitor_mode { kSCG_SysOscMonitorDisable = 0U , kSCG_SysOscMonitorInt = SCG_SOSCCSR_SOSCCM_MASK , kSCG_SysOscMonitorReset } |

| SCG system OSC monitor mode. More... | |

| enum | _scg_sosc_mode { kSCG_SysOscModeExt = 0U , kSCG_SysOscModeOscLowPower = SCG_SOSCCFG_EREFS_MASK , kSCG_SysOscModeOscHighGain = SCG_SOSCCFG_EREFS_MASK | SCG_SOSCCFG_HGO_MASK } |

| OSC work mode. More... | |

| enum | _scg_sosc_enable_mode { kSCG_SysOscEnable = SCG_SOSCCSR_SOSCEN_MASK , kSCG_SysOscEnableInStop = SCG_SOSCCSR_SOSCSTEN_MASK , kSCG_SysOscEnableInLowPower = SCG_SOSCCSR_SOSCLPEN_MASK , kSCG_SysOscEnableErClk = SCG_SOSCCSR_SOSCERCLKEN_MASK } |

| OSC enable mode. More... | |

| enum | _scg_sirc_range { kSCG_SircRangeLow , kSCG_SircRangeHigh } |

| SCG slow IRC clock frequency range. More... | |

| enum | _scg_sirc_enable_mode { kSCG_SircEnable = SCG_SIRCCSR_SIRCEN_MASK , kSCG_SircEnableInStop = SCG_SIRCCSR_SIRCSTEN_MASK , kSCG_SircEnableInLowPower = SCG_SIRCCSR_SIRCLPEN_MASK } |

| SIRC enable mode. More... | |

| enum | _scg_firc_trim_mode { kSCG_FircTrimNonUpdate = SCG_FIRCCSR_FIRCTREN_MASK , kSCG_FircTrimUpdate = SCG_FIRCCSR_FIRCTREN_MASK | SCG_FIRCCSR_FIRCTRUP_MASK } |

| SCG fast IRC trim mode. More... | |

| enum | _scg_firc_trim_div { kSCG_FircTrimDivBy1 , kSCG_FircTrimDivBy128 , kSCG_FircTrimDivBy256 , kSCG_FircTrimDivBy512 , kSCG_FircTrimDivBy1024 , kSCG_FircTrimDivBy2048 } |

| SCG fast IRC trim predivided value for system OSC. More... | |

| enum | _scg_firc_trim_src { kSCG_FircTrimSrcSysOsc = 2U } |

| SCG fast IRC trim source. More... | |

| enum | _scg_firc_range { kSCG_FircRange48M , kSCG_FircRange52M , kSCG_FircRange56M , kSCG_FircRange60M } |

| SCG fast IRC clock frequency range. More... | |

| enum | _scg_firc_enable_mode { kSCG_FircEnable = SCG_FIRCCSR_FIRCEN_MASK , kSCG_FircEnableInStop = SCG_FIRCCSR_FIRCSTEN_MASK , kSCG_FircEnableInLowPower = SCG_FIRCCSR_FIRCLPEN_MASK , kSCG_FircDisableRegulator = SCG_FIRCCSR_FIRCREGOFF_MASK } |

| FIRC enable mode. More... | |

| enum | _scg_spll_src { kSCG_SysPllSrcSysOsc , kSCG_SysPllSrcFirc } |

| SCG system PLL clock source. More... | |

| enum | _scg_spll_monitor_mode { kSCG_SysPllMonitorDisable = 0U , kSCG_SysPllMonitorInt = SCG_SPLLCSR_SPLLCM_MASK , kSCG_SysPllMonitorReset } |

| SCG system PLL monitor mode. More... | |

| enum | _scg_spll_enable_mode { kSCG_SysPllEnable = SCG_SPLLCSR_SPLLEN_MASK , kSCG_SysPllEnableInStop = SCG_SPLLCSR_SPLLSTEN_MASK } |

| SPLL enable mode. More... | |

| typedef enum _clock_name | clock_name_t |

| Clock name used to get clock frequency. | |

| typedef enum _clock_ip_src | clock_ip_src_t |

| Clock source for peripherals that support various clock selections. | |

| typedef enum _clock_ip_name | clock_ip_name_t |

| Peripheral clock name difinition used for clock gate, clock source and clock divider setting. It is defined as the corresponding register address. | |

| typedef enum _osc32_mode | osc32_mode_t |

| OSC32 work mode. | |

| typedef enum _scg_sys_clk | scg_sys_clk_t |

| SCG system clock type. | |

| typedef enum _scg_sys_clk_src | scg_sys_clk_src_t |

| SCG system clock source. | |

| typedef enum _scg_sys_clk_div | scg_sys_clk_div_t |

| SCG system clock divider value. | |

| typedef struct _scg_sys_clk_config | scg_sys_clk_config_t |

| SCG system clock configuration. | |

| typedef enum _clock_clkout_src | clock_clkout_src_t |

| SCG clock out configuration (CLKOUTSEL). | |

| typedef enum _scg_async_clk | scg_async_clk_t |

| SCG asynchronous clock type. | |

| typedef enum scg_async_clk_div | scg_async_clk_div_t |

| SCG asynchronous clock divider value. | |

| typedef enum _scg_sosc_monitor_mode | scg_sosc_monitor_mode_t |

| SCG system OSC monitor mode. | |

| typedef enum _scg_sosc_mode | scg_sosc_mode_t |

| OSC work mode. | |

| typedef struct _scg_sosc_config | scg_sosc_config_t |

| SCG system OSC configuration. | |

| typedef enum _scg_sirc_range | scg_sirc_range_t |

| SCG slow IRC clock frequency range. | |

| typedef struct _scg_sirc_config | scg_sirc_config_t |

| SCG slow IRC clock configuration. | |

| typedef enum _scg_firc_trim_mode | scg_firc_trim_mode_t |

| SCG fast IRC trim mode. | |

| typedef enum _scg_firc_trim_div | scg_firc_trim_div_t |

| SCG fast IRC trim predivided value for system OSC. | |

| typedef enum _scg_firc_trim_src | scg_firc_trim_src_t |

| SCG fast IRC trim source. | |

| typedef struct _scg_firc_trim_config | scg_firc_trim_config_t |

| SCG fast IRC clock trim configuration. | |

| typedef enum _scg_firc_range | scg_firc_range_t |

| SCG fast IRC clock frequency range. | |

| typedef struct _scg_firc_config_t | scg_firc_config_t |

| SCG fast IRC clock configuration. | |

| typedef enum _scg_spll_src | scg_spll_src_t |

| SCG system PLL clock source. | |

| typedef enum _scg_spll_monitor_mode | scg_spll_monitor_mode_t |

| SCG system PLL monitor mode. | |

| typedef struct _scg_spll_config | scg_spll_config_t |

| SCG system PLL configuration. | |

| volatile uint32_t | g_xtal0Freq |

| External XTAL0 (OSC0/SYSOSC) clock frequency. | |

| volatile uint32_t | g_xtal32Freq |

| External XTAL32/EXTAL32 clock frequency. | |

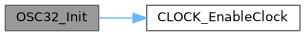

| static void | CLOCK_EnableClock (clock_ip_name_t name) |

| Enable the clock for specific IP. | |

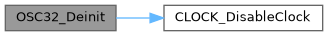

| static void | CLOCK_DisableClock (clock_ip_name_t name) |

| Disable the clock for specific IP. | |

| static bool | CLOCK_IsEnabledByOtherCore (clock_ip_name_t name) |

| Check whether the clock is already enabled and configured by any other core. | |

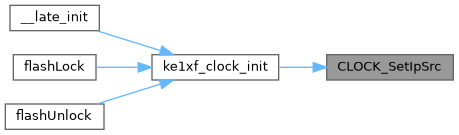

| static void | CLOCK_SetIpSrc (clock_ip_name_t name, clock_ip_src_t src) |

| Set the clock source for specific IP module. | |

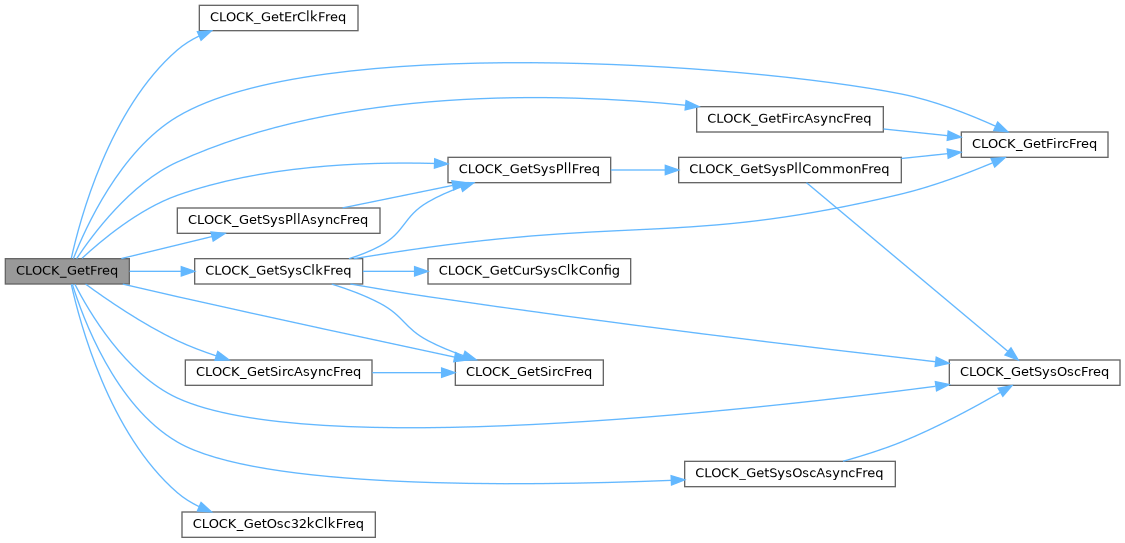

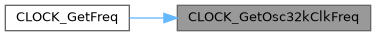

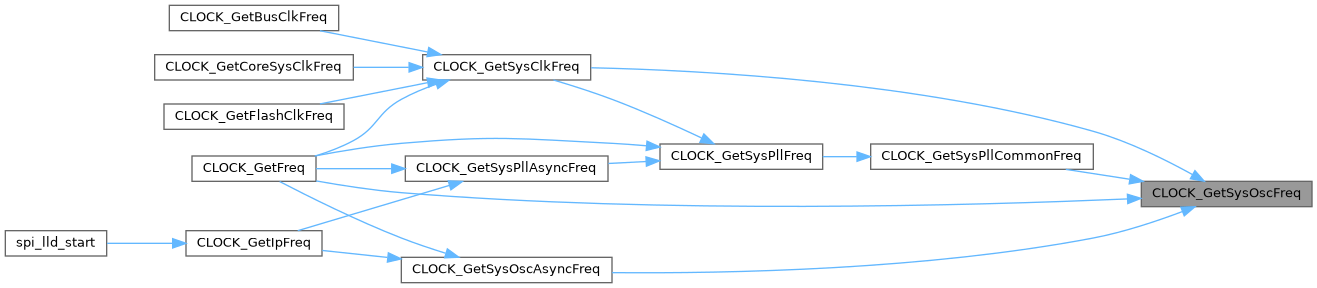

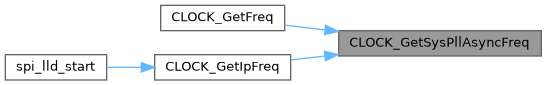

| uint32_t | CLOCK_GetFreq (clock_name_t clockName) |

| Gets the clock frequency for a specific clock name. | |

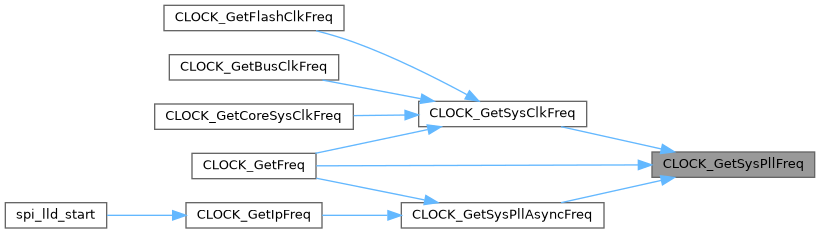

| uint32_t | CLOCK_GetCoreSysClkFreq (void) |

| Get the core clock or system clock frequency. | |

| uint32_t | CLOCK_GetBusClkFreq (void) |

| Get the bus clock frequency. | |

| uint32_t | CLOCK_GetFlashClkFreq (void) |

| Get the flash clock frequency. | |

| uint32_t | CLOCK_GetOsc32kClkFreq (void) |

| Get the OSC 32K clock frequency (OSC32KCLK). | |

| uint32_t | CLOCK_GetErClkFreq (void) |

| Get the external reference clock frequency (ERCLK). | |

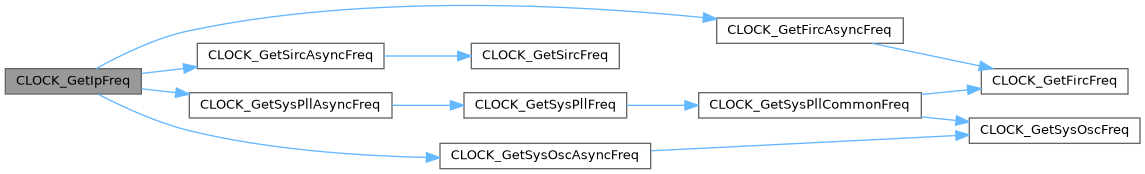

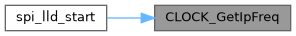

| uint32_t | CLOCK_GetIpFreq (clock_ip_name_t name) |

| Gets the clock frequency for a specific IP module. | |

MCU System Clock. | |

| uint32_t | CLOCK_GetSysClkFreq (scg_sys_clk_t type) |

| Gets the SCG system clock frequency. | |

| static void | CLOCK_SetVlprModeSysClkConfig (const scg_sys_clk_config_t *config) |

| Sets the system clock configuration for VLPR mode. | |

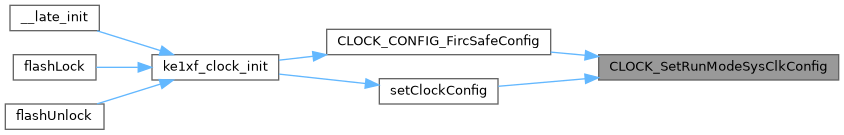

| static void | CLOCK_SetRunModeSysClkConfig (const scg_sys_clk_config_t *config) |

| Sets the system clock configuration for RUN mode. | |

| static void | CLOCK_SetHsrunModeSysClkConfig (const scg_sys_clk_config_t *config) |

| Sets the system clock configuration for HSRUN mode. | |

| static void | CLOCK_GetCurSysClkConfig (scg_sys_clk_config_t *config) |

| Gets the system clock configuration in the current power mode. | |

| static void | CLOCK_SetClkOutSel (clock_clkout_src_t setting) |

| Sets the clock out selection. | |

SCG System OSC Clock. | |

| status_t | CLOCK_InitSysOsc (const scg_sosc_config_t *config) |

| Initializes the SCG system OSC. | |

| status_t | CLOCK_DeinitSysOsc (void) |

| De-initializes the SCG system OSC. | |

| static void | CLOCK_SetSysOscAsyncClkDiv (scg_async_clk_t asyncClk, scg_async_clk_div_t divider) |

| Set the asynchronous clock divider. | |

| uint32_t | CLOCK_GetSysOscFreq (void) |

| Gets the SCG system OSC clock frequency (SYSOSC). | |

| uint32_t | CLOCK_GetSysOscAsyncFreq (scg_async_clk_t type) |

| Gets the SCG asynchronous clock frequency from the system OSC. | |

| static bool | CLOCK_IsSysOscErr (void) |

| Checks whether the system OSC clock error occurs. | |

| static void | CLOCK_ClearSysOscErr (void) |

| Clears the system OSC clock error. | |

| static void | CLOCK_SetSysOscMonitorMode (scg_sosc_monitor_mode_t mode) |

| Sets the system OSC monitor mode. | |

| static bool | CLOCK_IsSysOscValid (void) |

| Checks whether the system OSC clock is valid. | |

SCG Slow IRC Clock. | |

| status_t | CLOCK_InitSirc (const scg_sirc_config_t *config) |

| Initializes the SCG slow IRC clock. | |

| status_t | CLOCK_DeinitSirc (void) |

| De-initializes the SCG slow IRC. | |

| static void | CLOCK_SetSircAsyncClkDiv (scg_async_clk_t asyncClk, scg_async_clk_div_t divider) |

| Set the asynchronous clock divider. | |

| uint32_t | CLOCK_GetSircFreq (void) |

| Gets the SCG SIRC clock frequency. | |

| uint32_t | CLOCK_GetSircAsyncFreq (scg_async_clk_t type) |

| Gets the SCG asynchronous clock frequency from the SIRC. | |

| static bool | CLOCK_IsSircValid (void) |

| Checks whether the SIRC clock is valid. | |

SCG Fast IRC Clock. | |

| status_t | CLOCK_InitFirc (const scg_firc_config_t *config) |

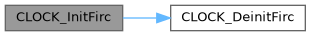

| Initializes the SCG fast IRC clock. | |

| status_t | CLOCK_DeinitFirc (void) |

| De-initializes the SCG fast IRC. | |

| static void | CLOCK_SetFircAsyncClkDiv (scg_async_clk_t asyncClk, scg_async_clk_div_t divider) |

| Set the asynchronous clock divider. | |

| uint32_t | CLOCK_GetFircFreq (void) |

| Gets the SCG FIRC clock frequency. | |

| uint32_t | CLOCK_GetFircAsyncFreq (scg_async_clk_t type) |

| Gets the SCG asynchronous clock frequency from the FIRC. | |

| static bool | CLOCK_IsFircErr (void) |

| Checks whether the FIRC clock error occurs. | |

| static void | CLOCK_ClearFircErr (void) |

| Clears the FIRC clock error. | |

| static bool | CLOCK_IsFircValid (void) |

| Checks whether the FIRC clock is valid. | |

SCG System PLL Clock. | |

| uint32_t | CLOCK_GetSysPllMultDiv (uint32_t refFreq, uint32_t desireFreq, uint8_t *mult, uint8_t *prediv) |

| Calculates the MULT and PREDIV for the PLL. | |

| status_t | CLOCK_InitSysPll (const scg_spll_config_t *config) |

| Initializes the SCG system PLL. | |

| status_t | CLOCK_DeinitSysPll (void) |

| De-initializes the SCG system PLL. | |

| static void | CLOCK_SetSysPllAsyncClkDiv (scg_async_clk_t asyncClk, scg_async_clk_div_t divider) |

| Set the asynchronous clock divider. | |

| uint32_t | CLOCK_GetSysPllFreq (void) |

| Gets the SCG system PLL clock frequency. | |

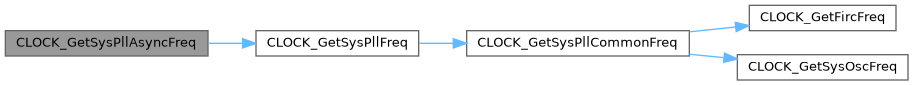

| uint32_t | CLOCK_GetSysPllAsyncFreq (scg_async_clk_t type) |

| Gets the SCG asynchronous clock frequency from the system PLL. | |

| static bool | CLOCK_IsSysPllErr (void) |

| Checks whether the system PLL clock error occurs. | |

| static void | CLOCK_ClearSysPllErr (void) |

| Clears the system PLL clock error. | |

| static void | CLOCK_SetSysPllMonitorMode (scg_spll_monitor_mode_t mode) |

| Sets the system PLL monitor mode. | |

| static bool | CLOCK_IsSysPllValid (void) |

| Checks whether the system PLL clock is valid. | |

OSC32 operations | |

| void | OSC32_Init (OSC32_Type *base, osc32_mode_t mode) |

| Initializes OSC32. | |

| void | OSC32_Deinit (OSC32_Type *base) |

| Deinitializes OSC32. | |

External clock frequency | |

| static void | CLOCK_SetXtal0Freq (uint32_t freq) |

| Sets the XTAL0 frequency based on board settings. | |

| static void | CLOCK_SetXtal32Freq (uint32_t freq) |

| Sets the XTAL32 frequency based on board settings. | |

Detailed Description

Typedef Documentation

◆ clock_clkout_src_t

| typedef enum _clock_clkout_src clock_clkout_src_t |

SCG clock out configuration (CLKOUTSEL).

◆ clock_ip_name_t

| typedef enum _clock_ip_name clock_ip_name_t |

Peripheral clock name difinition used for clock gate, clock source and clock divider setting. It is defined as the corresponding register address.

◆ clock_ip_src_t

| typedef enum _clock_ip_src clock_ip_src_t |

Clock source for peripherals that support various clock selections.

◆ clock_name_t

| typedef enum _clock_name clock_name_t |

Clock name used to get clock frequency.

◆ osc32_mode_t

| typedef enum _osc32_mode osc32_mode_t |

OSC32 work mode.

◆ scg_async_clk_div_t

| typedef enum scg_async_clk_div scg_async_clk_div_t |

SCG asynchronous clock divider value.

◆ scg_async_clk_t

| typedef enum _scg_async_clk scg_async_clk_t |

SCG asynchronous clock type.

◆ scg_firc_config_t

| typedef struct _scg_firc_config_t scg_firc_config_t |

SCG fast IRC clock configuration.

◆ scg_firc_range_t

| typedef enum _scg_firc_range scg_firc_range_t |

SCG fast IRC clock frequency range.

◆ scg_firc_trim_config_t

| typedef struct _scg_firc_trim_config scg_firc_trim_config_t |

SCG fast IRC clock trim configuration.

◆ scg_firc_trim_div_t

| typedef enum _scg_firc_trim_div scg_firc_trim_div_t |

SCG fast IRC trim predivided value for system OSC.

◆ scg_firc_trim_mode_t

| typedef enum _scg_firc_trim_mode scg_firc_trim_mode_t |

SCG fast IRC trim mode.

◆ scg_firc_trim_src_t

| typedef enum _scg_firc_trim_src scg_firc_trim_src_t |

SCG fast IRC trim source.

◆ scg_sirc_config_t

| typedef struct _scg_sirc_config scg_sirc_config_t |

SCG slow IRC clock configuration.

◆ scg_sirc_range_t

| typedef enum _scg_sirc_range scg_sirc_range_t |

SCG slow IRC clock frequency range.

◆ scg_sosc_config_t

| typedef struct _scg_sosc_config scg_sosc_config_t |

SCG system OSC configuration.

◆ scg_sosc_mode_t

| typedef enum _scg_sosc_mode scg_sosc_mode_t |

OSC work mode.

◆ scg_sosc_monitor_mode_t

| typedef enum _scg_sosc_monitor_mode scg_sosc_monitor_mode_t |

SCG system OSC monitor mode.

◆ scg_spll_config_t

| typedef struct _scg_spll_config scg_spll_config_t |

SCG system PLL configuration.

◆ scg_spll_monitor_mode_t

| typedef enum _scg_spll_monitor_mode scg_spll_monitor_mode_t |

SCG system PLL monitor mode.

◆ scg_spll_src_t

| typedef enum _scg_spll_src scg_spll_src_t |

SCG system PLL clock source.

◆ scg_sys_clk_config_t

| typedef struct _scg_sys_clk_config scg_sys_clk_config_t |

SCG system clock configuration.

◆ scg_sys_clk_div_t

| typedef enum _scg_sys_clk_div scg_sys_clk_div_t |

SCG system clock divider value.

◆ scg_sys_clk_src_t

| typedef enum _scg_sys_clk_src scg_sys_clk_src_t |

SCG system clock source.

◆ scg_sys_clk_t

| typedef enum _scg_sys_clk scg_sys_clk_t |

SCG system clock type.

Enumeration Type Documentation

◆ _clock_clkout_src

| enum _clock_clkout_src |

SCG clock out configuration (CLKOUTSEL).

| Enumerator | |

|---|---|

| kClockClkoutSelScgSlow | SCG slow clock. |

| kClockClkoutSelSysOsc | System OSC. |

| kClockClkoutSelSirc | Slow IRC. |

| kClockClkoutSelFirc | Fast IRC. |

| kClockClkoutSelSysPll | System PLL. |

Definition at line 395 of file fsl_clock.h.

◆ _clock_ip_name

| enum _clock_ip_name |

Peripheral clock name difinition used for clock gate, clock source and clock divider setting. It is defined as the corresponding register address.

Definition at line 266 of file fsl_clock.h.

◆ _clock_ip_src

| enum _clock_ip_src |

Clock source for peripherals that support various clock selections.

Definition at line 253 of file fsl_clock.h.

◆ _clock_name

| enum _clock_name |

Clock name used to get clock frequency.

Definition at line 213 of file fsl_clock.h.

◆ _osc32_mode

| enum _osc32_mode |

OSC32 work mode.

| Enumerator | |

|---|---|

| kOSC32_Bypass | Bypass mode, use external input clock directly. |

| kOSC32_Crystal | Crystal mode, does not work in stop mode. |

| kOSC32_CrystalEnableInStop | Crystal mode, still work in stop mode. |

Definition at line 316 of file fsl_clock.h.

◆ _scg_async_clk

| enum _scg_async_clk |

SCG asynchronous clock type.

| Enumerator | |

|---|---|

| kSCG_AsyncDiv1Clk | The async clock by DIV1, e.g. SOSCDIV1_CLK, SIRCDIV1_CLK. |

| kSCG_AsyncDiv2Clk | The async clock by DIV2, e.g. SOSCDIV2_CLK, SIRCDIV2_CLK. |

Definition at line 407 of file fsl_clock.h.

◆ _scg_firc_enable_mode

FIRC enable mode.

| Enumerator | |

|---|---|

| kSCG_FircEnable | Enable FIRC clock. |

| kSCG_FircEnableInStop | Enable FIRC in stop mode. |

| kSCG_FircEnableInLowPower | Enable FIRC in low power mode. |

| kSCG_FircDisableRegulator | Disable regulator. |

Definition at line 562 of file fsl_clock.h.

◆ _scg_firc_range

| enum _scg_firc_range |

SCG fast IRC clock frequency range.

Definition at line 553 of file fsl_clock.h.

◆ _scg_firc_trim_div

| enum _scg_firc_trim_div |

SCG fast IRC trim predivided value for system OSC.

Definition at line 519 of file fsl_clock.h.

◆ _scg_firc_trim_mode

| enum _scg_firc_trim_mode |

SCG fast IRC trim mode.

| Enumerator | |

|---|---|

| kSCG_FircTrimNonUpdate | FIRC trim enable but not enable trim value update. In this mode, the trim value is fixed to the initialized value which is defined by trimCoar and trimFine in configure structure scg_firc_trim_config_t. |

| kSCG_FircTrimUpdate | FIRC trim enable and trim value update enable. In this mode, the trim value is auto update. |

Definition at line 503 of file fsl_clock.h.

◆ _scg_firc_trim_src

| enum _scg_firc_trim_src |

SCG fast IRC trim source.

| Enumerator | |

|---|---|

| kSCG_FircTrimSrcSysOsc | System OSC. |

Definition at line 532 of file fsl_clock.h.

◆ _scg_sirc_enable_mode

SIRC enable mode.

| Enumerator | |

|---|---|

| kSCG_SircEnable | Enable SIRC clock. |

| kSCG_SircEnableInStop | Enable SIRC in stop mode. |

| kSCG_SircEnableInLowPower | Enable SIRC in low power mode. |

Definition at line 481 of file fsl_clock.h.

◆ _scg_sirc_range

| enum _scg_sirc_range |

SCG slow IRC clock frequency range.

| Enumerator | |

|---|---|

| kSCG_SircRangeLow | Slow IRC low range clock (2 MHz, 4 MHz for i.MX 7 ULP). |

| kSCG_SircRangeHigh | Slow IRC high range clock (8 MHz, 16 MHz for i.MX 7 ULP). |

Definition at line 474 of file fsl_clock.h.

◆ _scg_sosc_enable_mode

OSC enable mode.

| Enumerator | |

|---|---|

| kSCG_SysOscEnable | Enable OSC clock. |

| kSCG_SysOscEnableInStop | Enable OSC in stop mode. |

| kSCG_SysOscEnableInLowPower | Enable OSC in low power mode. |

| kSCG_SysOscEnableErClk | Enable OSCERCLK. |

Definition at line 448 of file fsl_clock.h.

◆ _scg_sosc_mode

| enum _scg_sosc_mode |

OSC work mode.

| Enumerator | |

|---|---|

| kSCG_SysOscModeExt | Use external clock. |

| kSCG_SysOscModeOscLowPower | Oscillator low power. |

| kSCG_SysOscModeOscHighGain | Oscillator high gain. |

Definition at line 440 of file fsl_clock.h.

◆ _scg_sosc_monitor_mode

SCG system OSC monitor mode.

| Enumerator | |

|---|---|

| kSCG_SysOscMonitorDisable | Monitor disabled. |

| kSCG_SysOscMonitorInt | Interrupt when the system OSC error is detected. |

| kSCG_SysOscMonitorReset | Reset when the system OSC error is detected. |

Definition at line 431 of file fsl_clock.h.

◆ _scg_spll_enable_mode

SPLL enable mode.

| Enumerator | |

|---|---|

| kSCG_SysPllEnable | Enable SPLL clock. |

| kSCG_SysPllEnableInStop | Enable SPLL in stop mode. |

Definition at line 606 of file fsl_clock.h.

◆ _scg_spll_monitor_mode

SCG system PLL monitor mode.

| Enumerator | |

|---|---|

| kSCG_SysPllMonitorDisable | Monitor disabled. |

| kSCG_SysPllMonitorInt | Interrupt when the system PLL error is detected. |

| kSCG_SysPllMonitorReset | Reset when the system PLL error is detected. |

Definition at line 597 of file fsl_clock.h.

◆ _scg_spll_src

| enum _scg_spll_src |

SCG system PLL clock source.

| Enumerator | |

|---|---|

| kSCG_SysPllSrcSysOsc | System PLL clock source is system OSC. |

| kSCG_SysPllSrcFirc | System PLL clock source is fast IRC. |

Definition at line 588 of file fsl_clock.h.

◆ _scg_status

| enum _scg_status |

SCG status return codes.

| Enumerator | |

|---|---|

| kStatus_SCG_Busy | Clock is busy. |

| kStatus_SCG_InvalidSrc | Invalid source. |

Definition at line 327 of file fsl_clock.h.

◆ _scg_sys_clk

| enum _scg_sys_clk |

SCG system clock type.

| Enumerator | |

|---|---|

| kSCG_SysClkSlow | System slow clock. |

| kSCG_SysClkBus | Bus clock. |

| kSCG_SysClkCore | Core clock. |

Definition at line 336 of file fsl_clock.h.

◆ _scg_sys_clk_div

| enum _scg_sys_clk_div |

SCG system clock divider value.

Definition at line 357 of file fsl_clock.h.

◆ _scg_sys_clk_src

| enum _scg_sys_clk_src |

SCG system clock source.

| Enumerator | |

|---|---|

| kSCG_SysClkSrcSysOsc | System OSC. |

| kSCG_SysClkSrcSirc | Slow IRC. |

| kSCG_SysClkSrcFirc | Fast IRC. |

| kSCG_SysClkSrcSysPll | System PLL. |

Definition at line 346 of file fsl_clock.h.

◆ scg_async_clk_div

| enum scg_async_clk_div |

SCG asynchronous clock divider value.

Definition at line 416 of file fsl_clock.h.

Function Documentation

◆ CLOCK_ClearFircErr()

|

inlinestatic |

Clears the FIRC clock error.

Definition at line 1140 of file fsl_clock.h.

◆ CLOCK_ClearSysOscErr()

|

inlinestatic |

Clears the system OSC clock error.

Definition at line 932 of file fsl_clock.h.

◆ CLOCK_ClearSysPllErr()

|

inlinestatic |

Clears the system PLL clock error.

Definition at line 1282 of file fsl_clock.h.

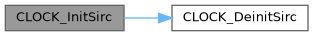

◆ CLOCK_DeinitFirc()

| status_t CLOCK_DeinitFirc | ( | void | ) |

De-initializes the SCG fast IRC.

This function disables the SCG fast IRC.

- Return values

-

kStatus_Success FIRC is deinitialized. kStatus_SCG_Busy FIRC is used by the system clock. kStatus_ReadOnly FIRC control register is locked.

- Note

- This function can't detect whether the FIRC is used by an IP.

brief De-initializes the SCG fast IRC.

This function disables the SCG fast IRC.

retval kStatus_Success FIRC is deinitialized. retval kStatus_SCG_Busy FIRC is used by the system clock. retval kStatus_ReadOnly FIRC control register is locked.

note This function can't detect whether the FIRC is used by an IP.

Definition at line 755 of file fsl_clock.c.

Referenced by CLOCK_InitFirc().

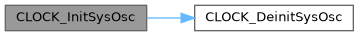

◆ CLOCK_DeinitSirc()

| status_t CLOCK_DeinitSirc | ( | void | ) |

De-initializes the SCG slow IRC.

This function disables the SCG slow IRC.

- Return values

-

kStatus_Success SIRC is deinitialized. kStatus_SCG_Busy SIRC is used by system clock. kStatus_ReadOnly SIRC control register is locked.

- Note

- This function can't detect whether the SIRC is used by an IP.

brief De-initializes the SCG slow IRC.

This function disables the SCG slow IRC.

retval kStatus_Success SIRC is deinitialized. retval kStatus_SCG_Busy SIRC is used by system clock. retval kStatus_ReadOnly SIRC control register is locked.

note This function can't detect whether the SIRC is used by an IP.

Definition at line 601 of file fsl_clock.c.

Referenced by CLOCK_InitSirc().

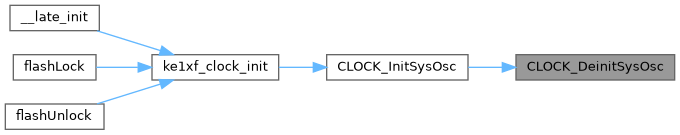

◆ CLOCK_DeinitSysOsc()

| status_t CLOCK_DeinitSysOsc | ( | void | ) |

De-initializes the SCG system OSC.

This function disables the SCG system OSC clock.

- Return values

-

kStatus_Success System OSC is deinitialized. kStatus_SCG_Busy System OSC is used by the system clock. kStatus_ReadOnly System OSC control register is locked.

- Note

- This function can't detect whether the system OSC is used by an IP.

brief De-initializes the SCG system OSC.

This function disables the SCG system OSC clock.

retval kStatus_Success System OSC is deinitialized. retval kStatus_SCG_Busy System OSC is used by the system clock. retval kStatus_ReadOnly System OSC control register is locked.

note This function can't detect whether the system OSC is used by an IP.

Definition at line 468 of file fsl_clock.c.

Referenced by CLOCK_InitSysOsc().

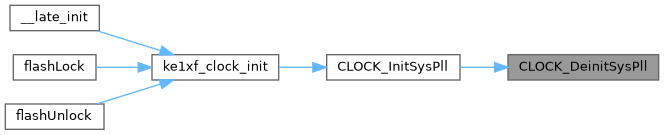

◆ CLOCK_DeinitSysPll()

| status_t CLOCK_DeinitSysPll | ( | void | ) |

De-initializes the SCG system PLL.

This function disables the SCG system PLL.

- Return values

-

kStatus_Success system PLL is deinitialized. kStatus_SCG_Busy system PLL is used by the system clock. kStatus_ReadOnly System PLL control register is locked.

- Note

- This function can't detect whether the system PLL is used by an IP.

brief De-initializes the SCG system PLL.

This function disables the SCG system PLL.

retval kStatus_Success system PLL is deinitialized. retval kStatus_SCG_Busy system PLL is used by the system clock. retval kStatus_ReadOnly System PLL control register is locked.

note This function can't detect whether the system PLL is used by an IP.

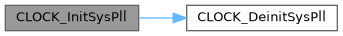

Definition at line 1031 of file fsl_clock.c.

Referenced by CLOCK_InitSysPll().

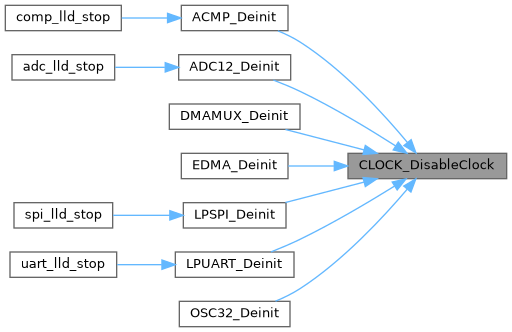

◆ CLOCK_DisableClock()

|

inlinestatic |

Disable the clock for specific IP.

- Parameters

-

name Which clock to disable, see clock_ip_name_t.

Definition at line 653 of file fsl_clock.h.

Referenced by ACMP_Deinit(), ADC12_Deinit(), DMAMUX_Deinit(), EDMA_Deinit(), LPSPI_Deinit(), LPUART_Deinit(), and OSC32_Deinit().

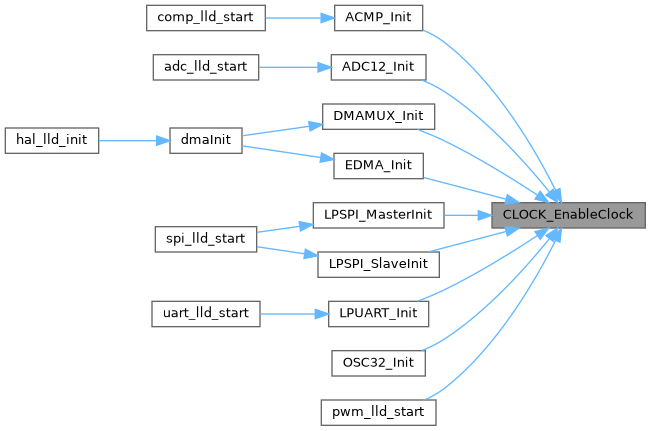

◆ CLOCK_EnableClock()

|

inlinestatic |

Enable the clock for specific IP.

- Parameters

-

name Which clock to enable, see clock_ip_name_t.

Definition at line 641 of file fsl_clock.h.

Referenced by ACMP_Init(), ADC12_Init(), DMAMUX_Init(), EDMA_Init(), LPSPI_MasterInit(), LPSPI_SlaveInit(), LPUART_Init(), OSC32_Init(), and pwm_lld_start().

◆ CLOCK_GetBusClkFreq()

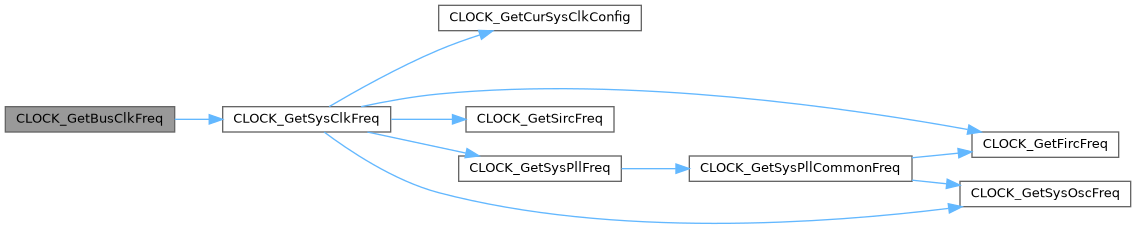

| uint32_t CLOCK_GetBusClkFreq | ( | void | ) |

Get the bus clock frequency.

- Returns

- Clock frequency in Hz.

brief Get the bus clock frequency.

return Clock frequency in Hz.

Definition at line 144 of file fsl_clock.c.

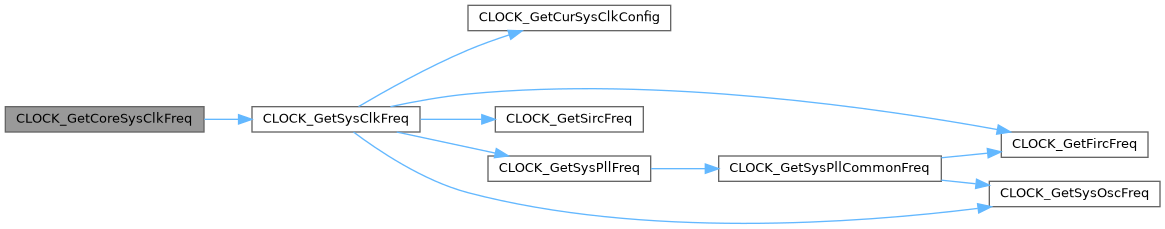

◆ CLOCK_GetCoreSysClkFreq()

| uint32_t CLOCK_GetCoreSysClkFreq | ( | void | ) |

Get the core clock or system clock frequency.

- Returns

- Clock frequency in Hz.

brief Get the core clock or system clock frequency.

return Clock frequency in Hz.

Definition at line 154 of file fsl_clock.c.

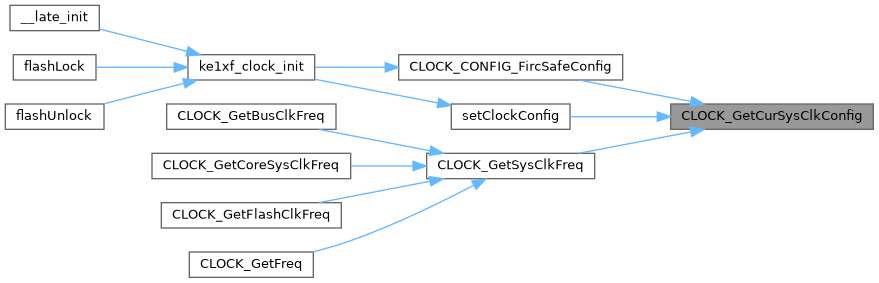

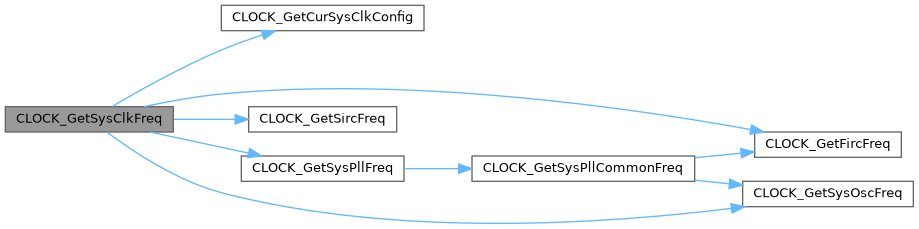

◆ CLOCK_GetCurSysClkConfig()

|

inlinestatic |

Gets the system clock configuration in the current power mode.

This function gets the system configuration in the current power mode.

- Parameters

-

config Pointer to the configuration.

Definition at line 823 of file fsl_clock.h.

Referenced by CLOCK_CONFIG_FircSafeConfig(), CLOCK_GetSysClkFreq(), and setClockConfig().

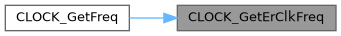

◆ CLOCK_GetErClkFreq()

| uint32_t CLOCK_GetErClkFreq | ( | void | ) |

Get the external reference clock frequency (ERCLK).

- Returns

- Clock frequency in Hz.

brief Get the external reference clock frequency (ERCLK).

return Clock frequency in Hz.

Definition at line 104 of file fsl_clock.c.

Referenced by CLOCK_GetFreq().

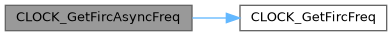

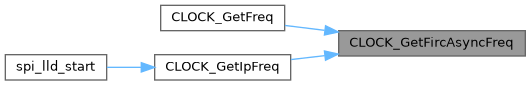

◆ CLOCK_GetFircAsyncFreq()

| uint32_t CLOCK_GetFircAsyncFreq | ( | scg_async_clk_t | type | ) |

Gets the SCG asynchronous clock frequency from the FIRC.

- Parameters

-

type The asynchronous clock type.

- Returns

- Clock frequency; If the clock is invalid, returns 0.

brief Gets the SCG asynchronous clock frequency from the FIRC.

param type The asynchronous clock type. return Clock frequency; If the clock is invalid, returns 0.

Definition at line 803 of file fsl_clock.c.

Referenced by CLOCK_GetFreq(), and CLOCK_GetIpFreq().

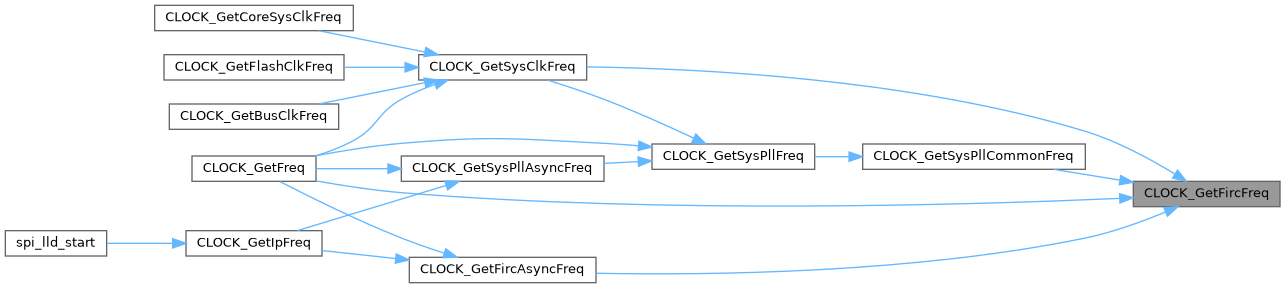

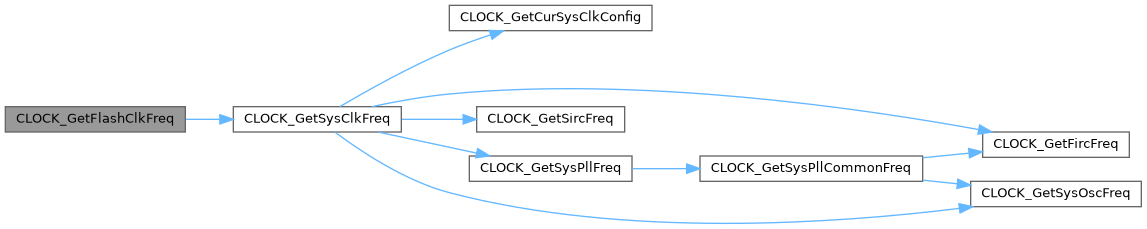

◆ CLOCK_GetFircFreq()

| uint32_t CLOCK_GetFircFreq | ( | void | ) |

Gets the SCG FIRC clock frequency.

- Returns

- Clock frequency; If the clock is invalid, returns 0.

brief Gets the SCG FIRC clock frequency.

return Clock frequency; If the clock is invalid, returns 0.

Definition at line 781 of file fsl_clock.c.

Referenced by CLOCK_GetFircAsyncFreq(), CLOCK_GetFreq(), CLOCK_GetSysClkFreq(), and CLOCK_GetSysPllCommonFreq().

◆ CLOCK_GetFlashClkFreq()

| uint32_t CLOCK_GetFlashClkFreq | ( | void | ) |

Get the flash clock frequency.

- Returns

- Clock frequency in Hz.

brief Get the flash clock frequency.

return Clock frequency in Hz.

Definition at line 134 of file fsl_clock.c.

◆ CLOCK_GetFreq()

| uint32_t CLOCK_GetFreq | ( | clock_name_t | clockName | ) |

Gets the clock frequency for a specific clock name.

This function checks the current clock configurations and then calculates the clock frequency for a specific clock name defined in clock_name_t.

- Parameters

-

clockName Clock names defined in clock_name_t

- Returns

- Clock frequency value in hertz

brief Gets the clock frequency for a specific clock name.

This function checks the current clock configurations and then calculates the clock frequency for a specific clock name defined in clock_name_t.

param clockName Clock names defined in clock_name_t return Clock frequency value in hertz

Definition at line 168 of file fsl_clock.c.

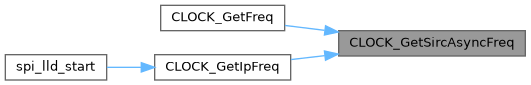

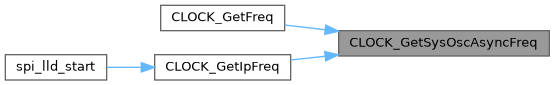

◆ CLOCK_GetIpFreq()

| uint32_t CLOCK_GetIpFreq | ( | clock_ip_name_t | name | ) |

Gets the clock frequency for a specific IP module.

This function gets the IP module clock frequency based on PCC registers. It is only used for the IP modules which could select clock source by PCC[PCS].

- Parameters

-

name Which peripheral to get, see clock_ip_name_t.

- Returns

- Clock frequency value in hertz

brief Gets the clock frequency for a specific IP module.

This function gets the IP module clock frequency based on PCC registers. It is only used for the IP modules which could select clock source by PCC[PCS].

param name Which peripheral to get, see clock_ip_name_t. return Clock frequency value in hertz

Definition at line 250 of file fsl_clock.c.

Referenced by spi_lld_start().

◆ CLOCK_GetOsc32kClkFreq()

| uint32_t CLOCK_GetOsc32kClkFreq | ( | void | ) |

Get the OSC 32K clock frequency (OSC32KCLK).

- Returns

- Clock frequency in Hz.

brief Get the OSC 32K clock frequency (OSC32KCLK).

return Clock frequency in Hz.

Definition at line 123 of file fsl_clock.c.

Referenced by CLOCK_GetFreq().

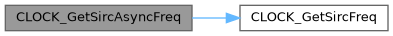

◆ CLOCK_GetSircAsyncFreq()

| uint32_t CLOCK_GetSircAsyncFreq | ( | scg_async_clk_t | type | ) |

Gets the SCG asynchronous clock frequency from the SIRC.

- Parameters

-

type The asynchronous clock type.

- Returns

- Clock frequency; If the clock is invalid, returns 0.

brief Gets the SCG asynchronous clock frequency from the SIRC.

param type The asynchronous clock type. return Clock frequency; If the clock is invalid, returns 0.

Definition at line 647 of file fsl_clock.c.

Referenced by CLOCK_GetFreq(), and CLOCK_GetIpFreq().

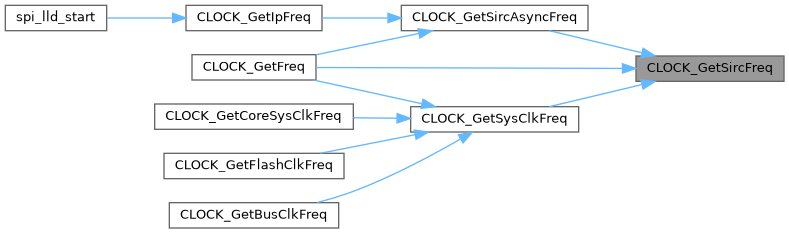

◆ CLOCK_GetSircFreq()

| uint32_t CLOCK_GetSircFreq | ( | void | ) |

Gets the SCG SIRC clock frequency.

- Returns

- Clock frequency; If the clock is invalid, returns 0.

brief Gets the SCG SIRC clock frequency.

return Clock frequency; If the clock is invalid, returns 0.

Definition at line 627 of file fsl_clock.c.

Referenced by CLOCK_GetFreq(), CLOCK_GetSircAsyncFreq(), and CLOCK_GetSysClkFreq().

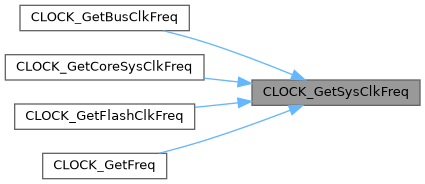

◆ CLOCK_GetSysClkFreq()

| uint32_t CLOCK_GetSysClkFreq | ( | scg_sys_clk_t | type | ) |

Gets the SCG system clock frequency.

This function gets the SCG system clock frequency. These clocks are used for core, platform, external, and bus clock domains.

- Parameters

-

type Which type of clock to get, core clock or slow clock.

- Returns

- Clock frequency.

brief Gets the SCG system clock frequency.

This function gets the SCG system clock frequency. These clocks are used for core, platform, external, and bus clock domains.

param type Which type of clock to get, core clock or slow clock. return Clock frequency.

Definition at line 339 of file fsl_clock.c.

Referenced by CLOCK_GetBusClkFreq(), CLOCK_GetCoreSysClkFreq(), CLOCK_GetFlashClkFreq(), and CLOCK_GetFreq().

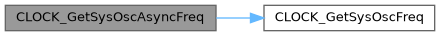

◆ CLOCK_GetSysOscAsyncFreq()

| uint32_t CLOCK_GetSysOscAsyncFreq | ( | scg_async_clk_t | type | ) |

Gets the SCG asynchronous clock frequency from the system OSC.

- Parameters

-

type The asynchronous clock type.

- Returns

- Clock frequency; If the clock is invalid, returns 0.

brief Gets the SCG asynchronous clock frequency from the system OSC.

param type The asynchronous clock type. return Clock frequency; If the clock is invalid, returns 0.

Definition at line 514 of file fsl_clock.c.

Referenced by CLOCK_GetFreq(), and CLOCK_GetIpFreq().

◆ CLOCK_GetSysOscFreq()

| uint32_t CLOCK_GetSysOscFreq | ( | void | ) |

Gets the SCG system OSC clock frequency (SYSOSC).

- Returns

- Clock frequency; If the clock is invalid, returns 0.

brief Gets the SCG system OSC clock frequency (SYSOSC).

return Clock frequency; If the clock is invalid, returns 0.

Definition at line 494 of file fsl_clock.c.

Referenced by CLOCK_GetFreq(), CLOCK_GetSysClkFreq(), CLOCK_GetSysOscAsyncFreq(), and CLOCK_GetSysPllCommonFreq().

◆ CLOCK_GetSysPllAsyncFreq()

| uint32_t CLOCK_GetSysPllAsyncFreq | ( | scg_async_clk_t | type | ) |

Gets the SCG asynchronous clock frequency from the system PLL.

- Parameters

-

type The asynchronous clock type.

- Returns

- Clock frequency; If the clock is invalid, returns 0.

brief Gets the SCG asynchronous clock frequency from the system PLL.

param type The asynchronous clock type. return Clock frequency; If the clock is invalid, returns 0.

Definition at line 1102 of file fsl_clock.c.

Referenced by CLOCK_GetFreq(), and CLOCK_GetIpFreq().

◆ CLOCK_GetSysPllFreq()

| uint32_t CLOCK_GetSysPllFreq | ( | void | ) |

Gets the SCG system PLL clock frequency.

- Returns

- Clock frequency; If the clock is invalid, returns 0.

brief Gets the SCG system PLL clock frequency.

return Clock frequency; If the clock is invalid, returns 0.

Definition at line 1080 of file fsl_clock.c.

Referenced by CLOCK_GetFreq(), CLOCK_GetSysClkFreq(), and CLOCK_GetSysPllAsyncFreq().

◆ CLOCK_GetSysPllMultDiv()

| uint32_t CLOCK_GetSysPllMultDiv | ( | uint32_t | refFreq, |

| uint32_t | desireFreq, | ||

| uint8_t * | mult, | ||

| uint8_t * | prediv | ||

| ) |

Calculates the MULT and PREDIV for the PLL.

This function calculates the proper MULT and PREDIV to generate the desired PLL output frequency with the input reference clock frequency. It returns the closest frequency match that the PLL can generate. The corresponding MULT/PREDIV are returned with parameters. If the desired frequency is not valid, this function returns 0.

- Parameters

-

refFreq The input reference clock frequency. desireFreq The desired output clock frequency. mult The value of MULT. prediv The value of PREDIV.

- Returns

- The PLL output frequency with the MULT and PREDIV; If the desired frequency can't be generated, this function returns 0U.

brief Calculates the MULT and PREDIV for the PLL.

This function calculates the proper MULT and PREDIV to generate the desired PLL output frequency with the input reference clock frequency. It returns the closest frequency match that the PLL can generate. The corresponding MULT/PREDIV are returned with parameters. If the desired frequency is not valid, this function returns 0.

param refFreq The input reference clock frequency. param desireFreq The desired output clock frequency. param mult The value of MULT. param prediv The value of PREDIV. return The PLL output frequency with the MULT and PREDIV; If the desired frequency can't be generated, this function returns 0U.

Definition at line 848 of file fsl_clock.c.

◆ CLOCK_InitFirc()

| status_t CLOCK_InitFirc | ( | const scg_firc_config_t * | config | ) |

Initializes the SCG fast IRC clock.

This function enables the SCG fast IRC clock according to the configuration.

- Parameters

-

config Pointer to the configuration structure.

- Return values

-

kStatus_Success FIRC is initialized. kStatus_SCG_Busy FIRC has been enabled and is used by the system clock. kStatus_ReadOnly FIRC control register is locked.

- Note

- This function can't detect whether the FIRC has been enabled and used by an IP.

brief Initializes the SCG fast IRC clock.

This function enables the SCG fast IRC clock according to the configuration.

param config Pointer to the configuration structure. retval kStatus_Success FIRC is initialized. retval kStatus_SCG_Busy FIRC has been enabled and is used by the system clock. retval kStatus_ReadOnly FIRC control register is locked.

note This function can't detect whether the FIRC has been enabled and used by an IP.

Definition at line 690 of file fsl_clock.c.

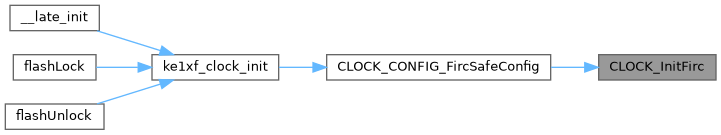

Referenced by CLOCK_CONFIG_FircSafeConfig().

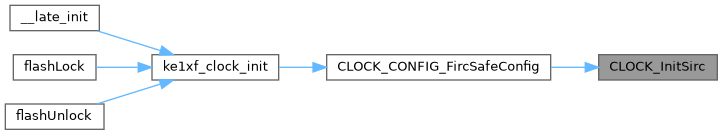

◆ CLOCK_InitSirc()

| status_t CLOCK_InitSirc | ( | const scg_sirc_config_t * | config | ) |

Initializes the SCG slow IRC clock.

This function enables the SCG slow IRC clock according to the configuration.

- Parameters

-

config Pointer to the configuration structure.

- Return values

-

kStatus_Success SIRC is initialized. kStatus_SCG_Busy SIRC has been enabled and is used by system clock. kStatus_ReadOnly SIRC control register is locked.

- Note

- This function can't detect whether the system OSC has been enabled and used by an IP.

brief Initializes the SCG slow IRC clock.

This function enables the SCG slow IRC clock according to the configuration.

param config Pointer to the configuration structure. retval kStatus_Success SIRC is initialized. retval kStatus_SCG_Busy SIRC has been enabled and is used by system clock. retval kStatus_ReadOnly SIRC control register is locked.

note This function can't detect whether the system OSC has been enabled and used by an IP.

Definition at line 558 of file fsl_clock.c.

Referenced by CLOCK_CONFIG_FircSafeConfig().

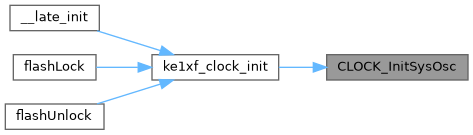

◆ CLOCK_InitSysOsc()

| status_t CLOCK_InitSysOsc | ( | const scg_sosc_config_t * | config | ) |

Initializes the SCG system OSC.

This function enables the SCG system OSC clock according to the configuration.

- Parameters

-

config Pointer to the configuration structure.

- Return values

-

kStatus_Success System OSC is initialized. kStatus_SCG_Busy System OSC has been enabled and is used by the system clock. kStatus_ReadOnly System OSC control register is locked.

- Note

- This function can't detect whether the system OSC has been enabled and used by an IP.

brief Initializes the SCG system OSC.

This function enables the SCG system OSC clock according to the configuration.

param config Pointer to the configuration structure. retval kStatus_Success System OSC is initialized. retval kStatus_SCG_Busy System OSC has been enabled and is used by the system clock. retval kStatus_ReadOnly System OSC control register is locked.

note This function can't detect whether the system OSC has been enabled and used by an IP.

Definition at line 397 of file fsl_clock.c.

Referenced by ke1xf_clock_init().

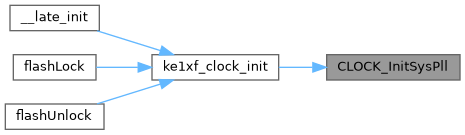

◆ CLOCK_InitSysPll()

| status_t CLOCK_InitSysPll | ( | const scg_spll_config_t * | config | ) |

Initializes the SCG system PLL.

This function enables the SCG system PLL clock according to the configuration. The system PLL can use the system OSC or FIRC as the clock source. Ensure that the source clock is valid before calling this function.

Example code for initializing SPLL clock output:

- Parameters

-

config Pointer to the configuration structure.

- Return values

-

kStatus_Success System PLL is initialized. kStatus_SCG_Busy System PLL has been enabled and is used by the system clock. kStatus_ReadOnly System PLL control register is locked.

- Note

- This function can't detect whether the system PLL has been enabled and used by an IP.

brief Initializes the SCG system PLL.

This function enables the SCG system PLL clock according to the configuration. The system PLL can use the system OSC or FIRC as the clock source. Ensure that the source clock is valid before calling this function.

Example code for initializing SPLL clock output: code const scg_spll_config_t g_scgSysPllConfig = {.enableMode = kSCG_SysPllEnable, .monitorMode = kSCG_SysPllMonitorDisable, .div1 = kSCG_AsyncClkDivBy1, .div2 = kSCG_AsyncClkDisable, .div3 = kSCG_AsyncClkDivBy2, .src = kSCG_SysPllSrcFirc, .isBypassSelected = false, .isPfdSelected = false, // Configure SPLL PFD as diabled .prediv = 5U, .pfdClkout = kSCG_AuxPllPfd0Clk, // No need to configure pfdClkout; only needed for initialization .mult = 20U, .pllPostdiv1 = kSCG_SysClkDivBy3, .pllPostdiv2 = kSCG_SysClkDivBy4}; CLOCK_InitSysPll(&g_scgSysPllConfig); endcode

param config Pointer to the configuration structure. retval kStatus_Success System PLL is initialized. retval kStatus_SCG_Busy System PLL has been enabled and is used by the system clock. retval kStatus_ReadOnly System PLL control register is locked.

note This function can't detect whether the system PLL has been enabled and used by an IP.

Definition at line 984 of file fsl_clock.c.

Referenced by ke1xf_clock_init().

◆ CLOCK_IsEnabledByOtherCore()

|

inlinestatic |

Check whether the clock is already enabled and configured by any other core.

- Parameters

-

name Which peripheral to check, see clock_ip_name_t.

- Returns

- True if clock is already enabled, otherwise false.

Definition at line 667 of file fsl_clock.h.

◆ CLOCK_IsFircErr()

|

inlinestatic |

Checks whether the FIRC clock error occurs.

- Returns

- True if the error occurs, false if not.

Definition at line 1132 of file fsl_clock.h.

◆ CLOCK_IsFircValid()

|

inlinestatic |

Checks whether the FIRC clock is valid.

- Returns

- True if clock is valid, false if not.

Definition at line 1150 of file fsl_clock.h.

◆ CLOCK_IsSircValid()

|

inlinestatic |

Checks whether the SIRC clock is valid.

- Returns

- True if clock is valid, false if not.

Definition at line 1047 of file fsl_clock.h.

◆ CLOCK_IsSysOscErr()

|

inlinestatic |

Checks whether the system OSC clock error occurs.

- Returns

- True if the error occurs, false if not.

Definition at line 924 of file fsl_clock.h.

◆ CLOCK_IsSysOscValid()

|

inlinestatic |

Checks whether the system OSC clock is valid.

- Returns

- True if clock is valid, false if not.

Definition at line 961 of file fsl_clock.h.

◆ CLOCK_IsSysPllErr()

|

inlinestatic |

Checks whether the system PLL clock error occurs.

- Returns

- True if an error occurs, false if not.

Definition at line 1274 of file fsl_clock.h.

◆ CLOCK_IsSysPllValid()

|

inlinestatic |

Checks whether the system PLL clock is valid.

- Returns

- True if the clock is valid, false if not.

Definition at line 1311 of file fsl_clock.h.

◆ CLOCK_SetClkOutSel()

|

inlinestatic |

Sets the clock out selection.

This function sets the clock out selection (CLKOUTSEL).

- Parameters

-

setting The selection to set.

- Returns

- The current clock out selection.

Definition at line 838 of file fsl_clock.h.

◆ CLOCK_SetFircAsyncClkDiv()

|

inlinestatic |

Set the asynchronous clock divider.

- Parameters

-

asyncClk Which asynchronous clock to configure. divider The divider value to set.

- Note

- There might be glitch when changing the asynchronous divider, so make sure the asynchronous clock is not used while changing divider.

Definition at line 1095 of file fsl_clock.h.

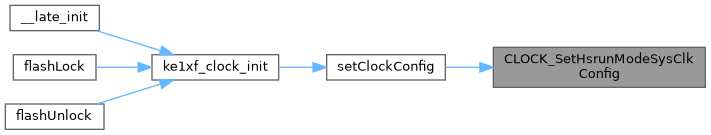

◆ CLOCK_SetHsrunModeSysClkConfig()

|

inlinestatic |

Sets the system clock configuration for HSRUN mode.

This function sets the system clock configuration for HSRUN mode.

- Parameters

-

config Pointer to the configuration.

Definition at line 809 of file fsl_clock.h.

Referenced by setClockConfig().

◆ CLOCK_SetIpSrc()

|

inlinestatic |

Set the clock source for specific IP module.

Set the clock source for specific IP, not all modules need to set the clock source, should only use this function for the modules need source setting.

- Parameters

-

name Which peripheral to check, see clock_ip_name_t. src Clock source to set.

Definition at line 684 of file fsl_clock.h.

Referenced by ke1xf_clock_init().

◆ CLOCK_SetRunModeSysClkConfig()

|

inlinestatic |

Sets the system clock configuration for RUN mode.

This function sets the system clock configuration for RUN mode.

- Parameters

-

config Pointer to the configuration.

Definition at line 795 of file fsl_clock.h.

Referenced by CLOCK_CONFIG_FircSafeConfig(), and setClockConfig().

◆ CLOCK_SetSircAsyncClkDiv()

|

inlinestatic |

Set the asynchronous clock divider.

- Parameters

-

asyncClk Which asynchronous clock to configure. divider The divider value to set.

- Note

- There might be glitch when changing the asynchronous divider, so make sure the asynchronous clock is not used while changing divider.

Definition at line 1010 of file fsl_clock.h.

◆ CLOCK_SetSysOscAsyncClkDiv()

|

inlinestatic |

Set the asynchronous clock divider.

- Parameters

-

asyncClk Which asynchronous clock to configure. divider The divider value to set.

- Note

- There might be glitch when changing the asynchronous divider, so make sure the asynchronous clock is not used while changing divider.

Definition at line 887 of file fsl_clock.h.

◆ CLOCK_SetSysOscMonitorMode()

|

inlinestatic |

Sets the system OSC monitor mode.

This function sets the system OSC monitor mode. The mode can be disabled, it can generate an interrupt when the error is disabled, or reset when the error is detected.

- Parameters

-

mode Monitor mode to set.

Definition at line 945 of file fsl_clock.h.

◆ CLOCK_SetSysPllAsyncClkDiv()

|

inlinestatic |

Set the asynchronous clock divider.

- Parameters

-

asyncClk Which asynchronous clock to configure. divider The divider value to set.

- Note

- There might be glitch when changing the asynchronous divider, so make sure the asynchronous clock is not used while changing divider.

Definition at line 1237 of file fsl_clock.h.

◆ CLOCK_SetSysPllMonitorMode()

|

inlinestatic |

Sets the system PLL monitor mode.

This function sets the system PLL monitor mode. The mode can be disabled. It can generate an interrupt when the error is disabled, or reset when the error is detected.

- Parameters

-

mode Monitor mode to set.

Definition at line 1295 of file fsl_clock.h.

◆ CLOCK_SetVlprModeSysClkConfig()

|

inlinestatic |

Sets the system clock configuration for VLPR mode.

This function sets the system clock configuration for VLPR mode.

- Parameters

-

config Pointer to the configuration.

Definition at line 781 of file fsl_clock.h.

◆ CLOCK_SetXtal0Freq()

|

inlinestatic |

Sets the XTAL0 frequency based on board settings.

- Parameters

-

freq The XTAL0/EXTAL0 input clock frequency in Hz.

Definition at line 1347 of file fsl_clock.h.

Referenced by ke1xf_clock_init().

◆ CLOCK_SetXtal32Freq()

|

inlinestatic |

Sets the XTAL32 frequency based on board settings.

- Parameters

-

freq The XTAL32/EXTAL32 input clock frequency in Hz.

Definition at line 1357 of file fsl_clock.h.

◆ OSC32_Deinit()

| void OSC32_Deinit | ( | OSC32_Type * | base | ) |

Deinitializes OSC32.

- Parameters

-

base OSC32 peripheral base address.

brief Deinitializes OSC32.

param base OSC32 peripheral base address.

Definition at line 321 of file fsl_clock.c.

◆ OSC32_Init()

| void OSC32_Init | ( | OSC32_Type * | base, |

| osc32_mode_t | mode | ||

| ) |

Initializes OSC32.

- Parameters

-

base OSC32 peripheral base address. mode OSC32 work mode, see osc32_mode_t

brief Initializes OSC32.

param base OSC32 peripheral base address. param mode OSC32 work mode, see ref osc32_mode_t

Definition at line 297 of file fsl_clock.c.

Variable Documentation

◆ __pad0__

| uint32_t _scg_sys_clk_config::__pad0__ |

Reserved.

Definition at line 384 of file fsl_clock.h.

◆ __pad1__

| uint32_t _scg_sys_clk_config::__pad1__ |

Reserved.

Definition at line 385 of file fsl_clock.h.

◆ __pad2__

| uint32_t _scg_sys_clk_config::__pad2__ |

Reserved.

Definition at line 387 of file fsl_clock.h.

◆ __pad3__

| uint32_t _scg_sys_clk_config::__pad3__ |

reserved.

Definition at line 389 of file fsl_clock.h.

◆ div1 [1/4]

| scg_async_clk_div_t _scg_sosc_config::div1 |

SOSCDIV1 value.

Definition at line 465 of file fsl_clock.h.

◆ div1 [2/4]

| scg_async_clk_div_t _scg_sirc_config::div1 |

SIRCDIV1 value.

Definition at line 494 of file fsl_clock.h.

◆ div1 [3/4]

| scg_async_clk_div_t _scg_firc_config_t::div1 |

FIRCDIV1 value.

Definition at line 577 of file fsl_clock.h.

◆ div1 [4/4]

| scg_async_clk_div_t _scg_spll_config::div1 |

SPLLDIV1 value.

Definition at line 620 of file fsl_clock.h.

◆ div2 [1/4]

| scg_async_clk_div_t _scg_sosc_config::div2 |

SOSCDIV2 value.

Definition at line 466 of file fsl_clock.h.

◆ div2 [2/4]

| scg_async_clk_div_t _scg_sirc_config::div2 |

SIRCDIV2 value.

Definition at line 495 of file fsl_clock.h.

◆ div2 [3/4]

| scg_async_clk_div_t _scg_firc_config_t::div2 |

FIRCDIV2 value.

Definition at line 578 of file fsl_clock.h.

◆ div2 [4/4]

| scg_async_clk_div_t _scg_spll_config::div2 |

SPLLDIV2 value.

Definition at line 621 of file fsl_clock.h.

◆ divBus

| uint32_t _scg_sys_clk_config::divBus |

Bus clock divider, see scg_sys_clk_div_t.

Definition at line 383 of file fsl_clock.h.

Referenced by CLOCK_GetSysClkFreq().

◆ divCore

| uint32_t _scg_sys_clk_config::divCore |

Core clock divider, see scg_sys_clk_div_t.

Definition at line 386 of file fsl_clock.h.

Referenced by CLOCK_GetSysClkFreq().

◆ divSlow

| uint32_t _scg_sys_clk_config::divSlow |

Slow clock divider, see scg_sys_clk_div_t.

Definition at line 382 of file fsl_clock.h.

Referenced by CLOCK_CONFIG_FircSafeConfig(), and CLOCK_GetSysClkFreq().

◆ enableMode [1/4]

| uint8_t _scg_sosc_config::enableMode |

Enable mode, OR'ed value of _scg_sosc_enable_mode.

Definition at line 463 of file fsl_clock.h.

◆ enableMode [2/4]

| uint32_t _scg_sirc_config::enableMode |

Enable mode, OR'ed value of _scg_sirc_enable_mode.

Definition at line 493 of file fsl_clock.h.

Referenced by CLOCK_CONFIG_FircSafeConfig().

◆ enableMode [3/4]

| uint32_t _scg_firc_config_t::enableMode |

Enable mode, OR'ed value of _scg_firc_enable_mode.

Definition at line 575 of file fsl_clock.h.

◆ enableMode [4/4]

| uint8_t _scg_spll_config::enableMode |

Enable mode, OR'ed value of _scg_spll_enable_mode

Definition at line 617 of file fsl_clock.h.

◆ freq

| uint32_t _scg_sosc_config::freq |

◆ g_xtal0Freq

|

extern |

External XTAL0 (OSC0/SYSOSC) clock frequency.

The XTAL0/EXTAL0 (OSC0/SYSOSC) clock frequency in Hz. When the clock is set up, use the function CLOCK_SetXtal0Freq to set the value in the clock driver. For example, if XTAL0 is 8 MHz:

This is important for the multicore platforms where only one core needs to set up the OSC0/SYSOSC using CLOCK_InitSysOsc. All other cores need to call the CLOCK_SetXtal0Freq to get a valid clock frequency.

Definition at line 75 of file fsl_clock.c.

Referenced by CLOCK_GetErClkFreq(), CLOCK_GetSysOscFreq(), and CLOCK_SetXtal0Freq().

◆ g_xtal32Freq

|

extern |

External XTAL32/EXTAL32 clock frequency.

The XTAL32/EXTAL32 clock frequency in Hz. When the clock is set up, use the function CLOCK_SetXtal32Freq to set the value in the clock driver.

This is important for the multicore platforms where only one core needs to set up the clock. All other cores need to call the CLOCK_SetXtal32Freq to get a valid clock frequency.

Definition at line 77 of file fsl_clock.c.

Referenced by CLOCK_GetOsc32kClkFreq(), and CLOCK_SetXtal32Freq().

◆ monitorMode [1/2]

| scg_sosc_monitor_mode_t _scg_sosc_config::monitorMode |

Clock monitor mode selected.

Definition at line 462 of file fsl_clock.h.

◆ monitorMode [2/2]

| scg_spll_monitor_mode_t _scg_spll_config::monitorMode |

Clock monitor mode selected.

Definition at line 618 of file fsl_clock.h.

◆ mult

| uint8_t _scg_spll_config::mult |

System PLL multiplier.

Definition at line 625 of file fsl_clock.h.

◆ prediv

| uint8_t _scg_spll_config::prediv |

PLL reference clock divider.

Definition at line 624 of file fsl_clock.h.

◆ range [1/2]

| scg_sirc_range_t _scg_sirc_config::range |

Slow IRC frequency range.

Definition at line 497 of file fsl_clock.h.

◆ range [2/2]

| scg_firc_range_t _scg_firc_config_t::range |

Fast IRC frequency range.

Definition at line 580 of file fsl_clock.h.

◆ src [1/2]

| uint32_t _scg_sys_clk_config::src |

System clock source, see scg_sys_clk_src_t.

Definition at line 388 of file fsl_clock.h.

Referenced by CLOCK_CONFIG_FircSafeConfig(), CLOCK_GetSysClkFreq(), and setClockConfig().

◆ src [2/2]

| scg_spll_src_t _scg_spll_config::src |

Clock source.

Definition at line 623 of file fsl_clock.h.

◆ trimCoar

| uint8_t _scg_firc_trim_config::trimCoar |

Trim coarse value; Irrelevant if trimMode is kSCG_FircTrimUpdate.

Definition at line 546 of file fsl_clock.h.

◆ trimConfig

| const scg_firc_trim_config_t* _scg_firc_config_t::trimConfig |

Pointer to the FIRC trim configuration; set NULL to disable trim.

Definition at line 582 of file fsl_clock.h.

◆ trimDiv

| scg_firc_trim_div_t _scg_firc_trim_config::trimDiv |

Trim predivided value for the system OSC.

Definition at line 544 of file fsl_clock.h.

◆ trimFine

| uint8_t _scg_firc_trim_config::trimFine |

Trim fine value; Irrelevant if trimMode is kSCG_FircTrimUpdate.

Definition at line 547 of file fsl_clock.h.

◆ trimMode

| scg_firc_trim_mode_t _scg_firc_trim_config::trimMode |

FIRC trim mode.

Definition at line 542 of file fsl_clock.h.

◆ trimSrc

| scg_firc_trim_src_t _scg_firc_trim_config::trimSrc |

Trim source.

Definition at line 543 of file fsl_clock.h.

◆ workMode

| scg_sosc_mode_t _scg_sosc_config::workMode |

OSC work mode.

Definition at line 468 of file fsl_clock.h.