Functions | |

| static void | CLOCK_CONFIG_FircSafeConfig (const scg_firc_config_t *fircConfig) |

| static bool | ke1xf_clock_is_external (kinetis_clock_type_e ct) |

| static bool | ke1xf_clock_is_high_speed (kinetis_clock_type_e ct) |

| static void | setClockConfig (kinetis_clock_type_e ct) |

| void | ke1xf_clock_init (kinetis_clock_type_e ct) |

| This function executes the configuration of clocks. | |

| kinetis_clock_type_e | ke1xf_clock_get_current_type (void) |

Function Documentation

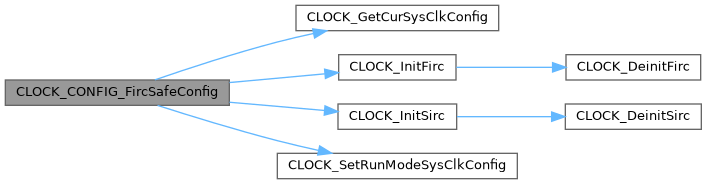

◆ CLOCK_CONFIG_FircSafeConfig()

|

static |

Definition at line 103 of file clock_config.c.

Referenced by ke1xf_clock_init().

◆ ke1xf_clock_get_current_type()

| kinetis_clock_type_e ke1xf_clock_get_current_type | ( | void | ) |

Definition at line 249 of file clock_config.c.

Referenced by flashUnlock().

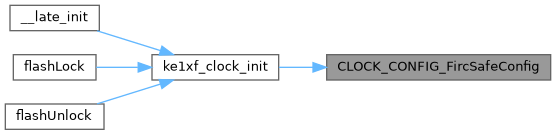

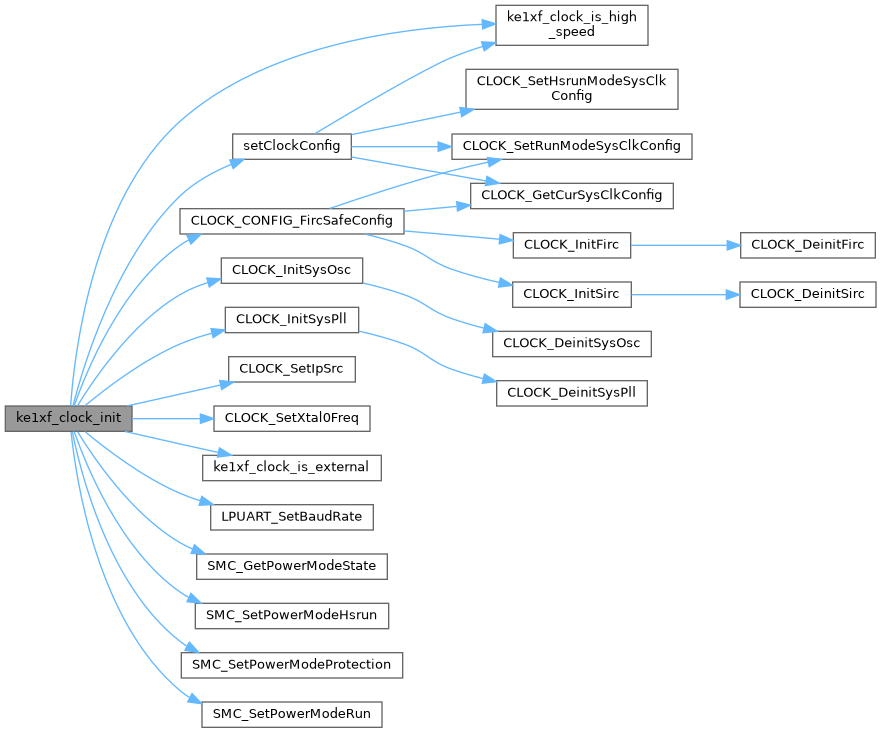

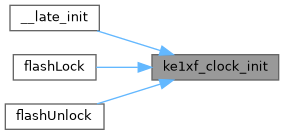

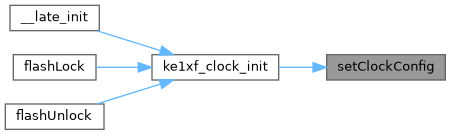

◆ ke1xf_clock_init()

| void ke1xf_clock_init | ( | kinetis_clock_type_e | ct | ) |

This function executes the configuration of clocks.

Definition at line 168 of file clock_config.c.

Referenced by __late_init(), flashLock(), and flashUnlock().

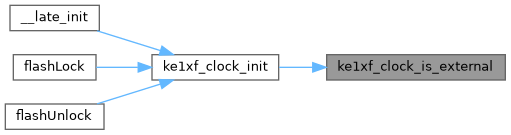

◆ ke1xf_clock_is_external()

|

static |

Definition at line 137 of file clock_config.c.

Referenced by ke1xf_clock_init().

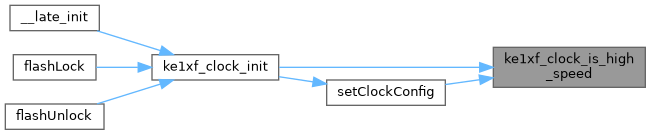

◆ ke1xf_clock_is_high_speed()

|

static |

Definition at line 141 of file clock_config.c.

Referenced by ke1xf_clock_init(), and setClockConfig().

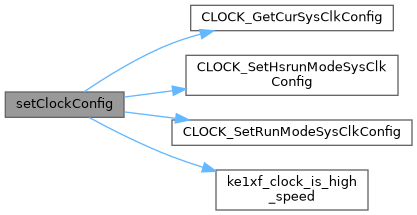

◆ setClockConfig()

|

static |

Definition at line 145 of file clock_config.c.

Referenced by ke1xf_clock_init().

Variable Documentation

◆ clockType

|

static |

Definition at line 26 of file clock_config.c.

Referenced by ke1xf_clock_get_current_type(), ke1xf_clock_init(), and setClockConfig().

◆ g_scgFircConfig_EXT_BOARD_BootClockRUN

| const scg_firc_config_t g_scgFircConfig_EXT_BOARD_BootClockRUN |

Definition at line 58 of file clock_config.c.

Referenced by ke1xf_clock_init().

◆ g_scgFircConfig_INT_BOARD_BootClockRUN

| const scg_firc_config_t g_scgFircConfig_INT_BOARD_BootClockRUN |

Definition at line 75 of file clock_config.c.

Referenced by ke1xf_clock_init().

◆ g_scgSircConfig_BOARD_BootClockRUN

| const scg_sirc_config_t g_scgSircConfig_BOARD_BootClockRUN |

Definition at line 52 of file clock_config.c.

◆ g_scgSysOscConfig_BOARD_BootClockRUN

| const scg_sosc_config_t g_scgSysOscConfig_BOARD_BootClockRUN |

Definition at line 44 of file clock_config.c.

Referenced by ke1xf_clock_init().

◆ g_scgSysPllConfig_EXT_BOARD_BootClockRUN

| const scg_spll_config_t g_scgSysPllConfig_EXT_BOARD_BootClockRUN |

Definition at line 65 of file clock_config.c.

Referenced by ke1xf_clock_init().

◆ g_scgSysPllConfig_INT_BOARD_BootClockRUN

| const scg_spll_config_t g_scgSysPllConfig_INT_BOARD_BootClockRUN |

Definition at line 82 of file clock_config.c.

Referenced by ke1xf_clock_init().

◆ g_sysClkConfig_BOARD_BootClockRUN

| const scg_sys_clk_config_t g_sysClkConfig_BOARD_BootClockRUN |

Definition at line 37 of file clock_config.c.

Referenced by setClockConfig().

◆ g_sysClkConfig_BOARD_BootClockRUN_HS

| const scg_sys_clk_config_t g_sysClkConfig_BOARD_BootClockRUN_HS |

Definition at line 29 of file clock_config.c.

Referenced by setClockConfig().