Enumerations | |

| enum | kinetis_clock_type_e { kinetis_clock_default_firc = 0 , kinetis_clock_int_osc_run , kinetis_clock_int_osc_hs , kinetis_clock_ext_osc_hs } |

| Kinetis Clock Type. More... | |

Functions | |

| void | ke1xf_clock_init (kinetis_clock_type_e clockType) |

| This function executes the configuration of clocks. | |

| kinetis_clock_type_e | ke1xf_clock_get_current_type (void) |

Enumeration Type Documentation

◆ kinetis_clock_type_e

| enum kinetis_clock_type_e |

Kinetis Clock Type.

| Enumerator | |

|---|---|

| kinetis_clock_default_firc | |

| kinetis_clock_int_osc_run | |

| kinetis_clock_int_osc_hs | |

| kinetis_clock_ext_osc_hs | |

Definition at line 9 of file clock_config.h.

Function Documentation

◆ ke1xf_clock_get_current_type()

| kinetis_clock_type_e ke1xf_clock_get_current_type | ( | void | ) |

Definition at line 249 of file clock_config.c.

249 {

251}

Referenced by flashUnlock().

Here is the caller graph for this function:

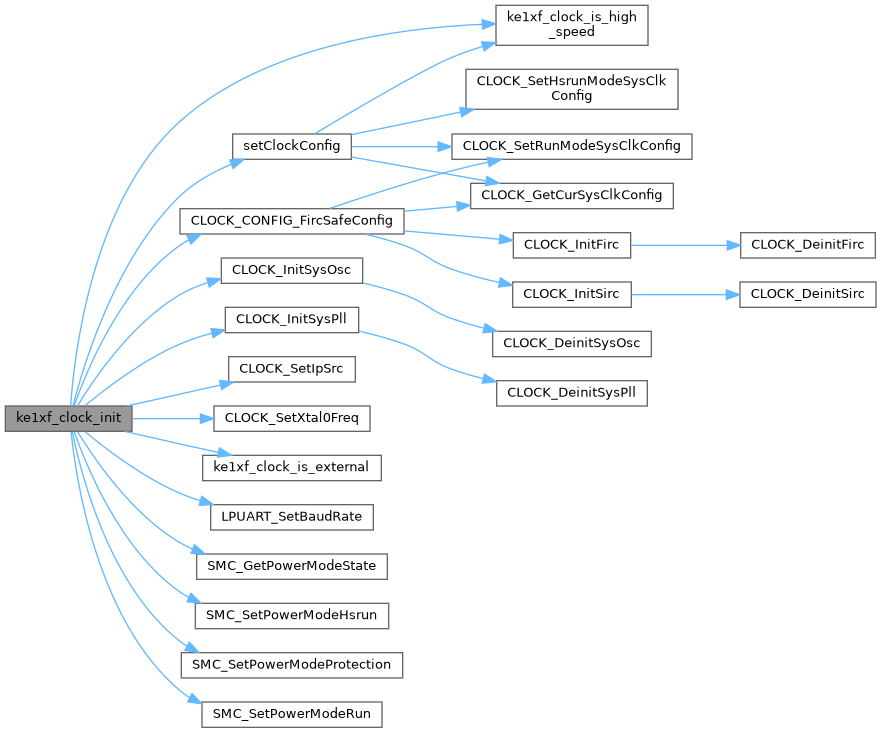

◆ ke1xf_clock_init()

| void ke1xf_clock_init | ( | kinetis_clock_type_e | clockType | ) |

This function executes the configuration of clocks.

Definition at line 168 of file clock_config.c.

168 {

169 // Init External Osc.

171 // Init SOSC according to board configuration.

173 // Set the XTAL0 frequency based on board settings.

175 }

176 // Init FIRC.

178 CLOCK_CONFIG_FircSafeConfig(ke1xf_clock_is_external(ct) ? &g_scgFircConfig_EXT_BOARD_BootClockRUN : &g_scgFircConfig_INT_BOARD_BootClockRUN);

179 }

180

182 // Set HSRUN power mode.

184 SMC_SetPowerModeHsrun(SMC);

186 }

187 } else {

188 // If we've already started and want to change the mode, then we have to lower the frequency first:

189 // [RTFM: "Before exiting HSRUN mode, clock frequencies should be reduced back down to those acceptable in RUN mode."]

191 setClockConfig(ct);

192 }

193

194 SMC_SetPowerModeRun(SMC);

196 }

197 }

198

199 // Now the mode is "officially" changed!

200 clockType = ct;

201

202 // Init SIRC.

203 //CLOCK_InitSirc(&g_scgSircConfig_BOARD_BootClockRUN);

204

205 // Init SysPll.

206 CLOCK_InitSysPll(ke1xf_clock_is_external(ct) ? &g_scgSysPllConfig_EXT_BOARD_BootClockRUN : &g_scgSysPllConfig_INT_BOARD_BootClockRUN);

207

208 // Set SCG to SPLL mode.

209 setClockConfig(ct);

210

211 /* Set SystemCoreClock variable. */

212 //SystemCoreClock = KINETIS_PLL_FREQ;

213

214 /* Set PCC ADC0 selection */

216 /* Set PCC ADC1 selection */

218 /* Set PCC ADC2 selection */

220 /* Set PCC LPSPI0 selection */

222 /* Set PCC LPSPI1 selection */

224 /* Set PCC LPUART0 selection */

226 /* Set PCC LPUART1 selection */

228 /* Set PCC LPTMR0 selection */

230 /* Set PCC LPIT0 selection */

232 /* Set PCC FTM0 selection */

234 /* Set PCC FTM1 selection */

236 /* Set PCC FTM2 selection */

238 /* Set PCC FTM3 selection */

240

241#if 0

243 // try to restore the UART if the frequency has been changed

244 LPUART_SetBaudRate(LPUART0, CLOCK_SYS_GetUartFreq(UART0_IDX), KINETIS_UART_FREQUENCY);

245 }

246#endif

247}

const scg_spll_config_t g_scgSysPllConfig_EXT_BOARD_BootClockRUN

Definition clock_config.c:65

const scg_firc_config_t g_scgFircConfig_EXT_BOARD_BootClockRUN

Definition clock_config.c:58

const scg_sosc_config_t g_scgSysOscConfig_BOARD_BootClockRUN

Definition clock_config.c:44

const scg_firc_config_t g_scgFircConfig_INT_BOARD_BootClockRUN

Definition clock_config.c:75

static void CLOCK_CONFIG_FircSafeConfig(const scg_firc_config_t *fircConfig)

Definition clock_config.c:103

static bool ke1xf_clock_is_high_speed(kinetis_clock_type_e ct)

Definition clock_config.c:141

const scg_spll_config_t g_scgSysPllConfig_INT_BOARD_BootClockRUN

Definition clock_config.c:82

static bool ke1xf_clock_is_external(kinetis_clock_type_e ct)

Definition clock_config.c:137

static void CLOCK_SetXtal0Freq(uint32_t freq)

Sets the XTAL0 frequency based on board settings.

Definition fsl_clock.h:1347

static void CLOCK_SetIpSrc(clock_ip_name_t name, clock_ip_src_t src)

Set the clock source for specific IP module.

Definition fsl_clock.h:684

status_t CLOCK_InitSysPll(const scg_spll_config_t *config)

Initializes the SCG system PLL.

Definition fsl_clock.c:984

status_t CLOCK_InitSysOsc(const scg_sosc_config_t *config)

Initializes the SCG system OSC.

Definition fsl_clock.c:397

status_t LPUART_SetBaudRate(LPUART_Type *base, uint32_t baudRate_Bps, uint32_t srcClock_Hz)

Sets the LPUART instance baudrate.

Definition fsl_lpuart.c:564

static void SMC_SetPowerModeProtection(SMC_Type *base, uint8_t allowedModes)

Configures all power mode protection settings.

Definition fsl_smc.h:260

static smc_power_state_t SMC_GetPowerModeState(SMC_Type *base)

Gets the current power mode status.

Definition fsl_smc.h:279

status_t SMC_SetPowerModeRun(SMC_Type *base)

Configures the system to RUN power mode.

Definition fsl_smc.c:147

status_t SMC_SetPowerModeHsrun(SMC_Type *base)

Configures the system to HSRUN power mode.

Definition fsl_smc.c:167

Referenced by __late_init(), flashLock(), and flashUnlock().

Here is the call graph for this function:

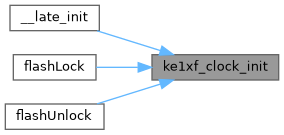

Here is the caller graph for this function: