Data Structures | |

| struct | _edma_config |

| eDMA global configuration structure. More... | |

| struct | _edma_transfer_config |

| eDMA transfer configuration More... | |

| struct | _edma_channel_Preemption_config |

| eDMA channel priority configuration More... | |

| struct | _edma_minor_offset_config |

| eDMA minor offset configuration More... | |

| struct | _edma_tcd |

| eDMA TCD. More... | |

| struct | _edma_handle |

| eDMA transfer handle structure More... | |

eDMA initialization and de-initialization | |

| void | EDMA_Init (DMA_Type *base, const edma_config_t *config) |

| Initializes the eDMA peripheral. | |

| void | EDMA_Deinit (DMA_Type *base) |

| Deinitializes the eDMA peripheral. | |

| void | EDMA_InstallTCD (DMA_Type *base, uint32_t channel, edma_tcd_t *tcd) |

| Push content of TCD structure into hardware TCD register. | |

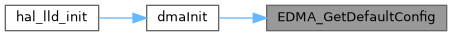

| void | EDMA_GetDefaultConfig (edma_config_t *config) |

| Gets the eDMA default configuration structure. | |

eDMA Channel Operation | |

| void | EDMA_ResetChannel (DMA_Type *base, uint32_t channel) |

| Sets all TCD registers to default values. | |

| void | EDMA_SetTransferConfig (DMA_Type *base, uint32_t channel, const edma_transfer_config_t *config, edma_tcd_t *nextTcd) |

| Configures the eDMA transfer attribute. | |

| void | EDMA_SetMinorOffsetConfig (DMA_Type *base, uint32_t channel, const edma_minor_offset_config_t *config) |

| Configures the eDMA minor offset feature. | |

| static void | EDMA_SetChannelPreemptionConfig (DMA_Type *base, uint32_t channel, const edma_channel_Preemption_config_t *config) |

| Configures the eDMA channel preemption feature. | |

| void | EDMA_SetChannelLink (DMA_Type *base, uint32_t channel, edma_channel_link_type_t type, uint32_t linkedChannel) |

| Sets the channel link for the eDMA transfer. | |

| void | EDMA_SetBandWidth (DMA_Type *base, uint32_t channel, edma_bandwidth_t bandWidth) |

| Sets the bandwidth for the eDMA transfer. | |

| void | EDMA_SetModulo (DMA_Type *base, uint32_t channel, edma_modulo_t srcModulo, edma_modulo_t destModulo) |

| Sets the source modulo and the destination modulo for the eDMA transfer. | |

| static void | EDMA_EnableAsyncRequest (DMA_Type *base, uint32_t channel, bool enable) |

| Enables an async request for the eDMA transfer. | |

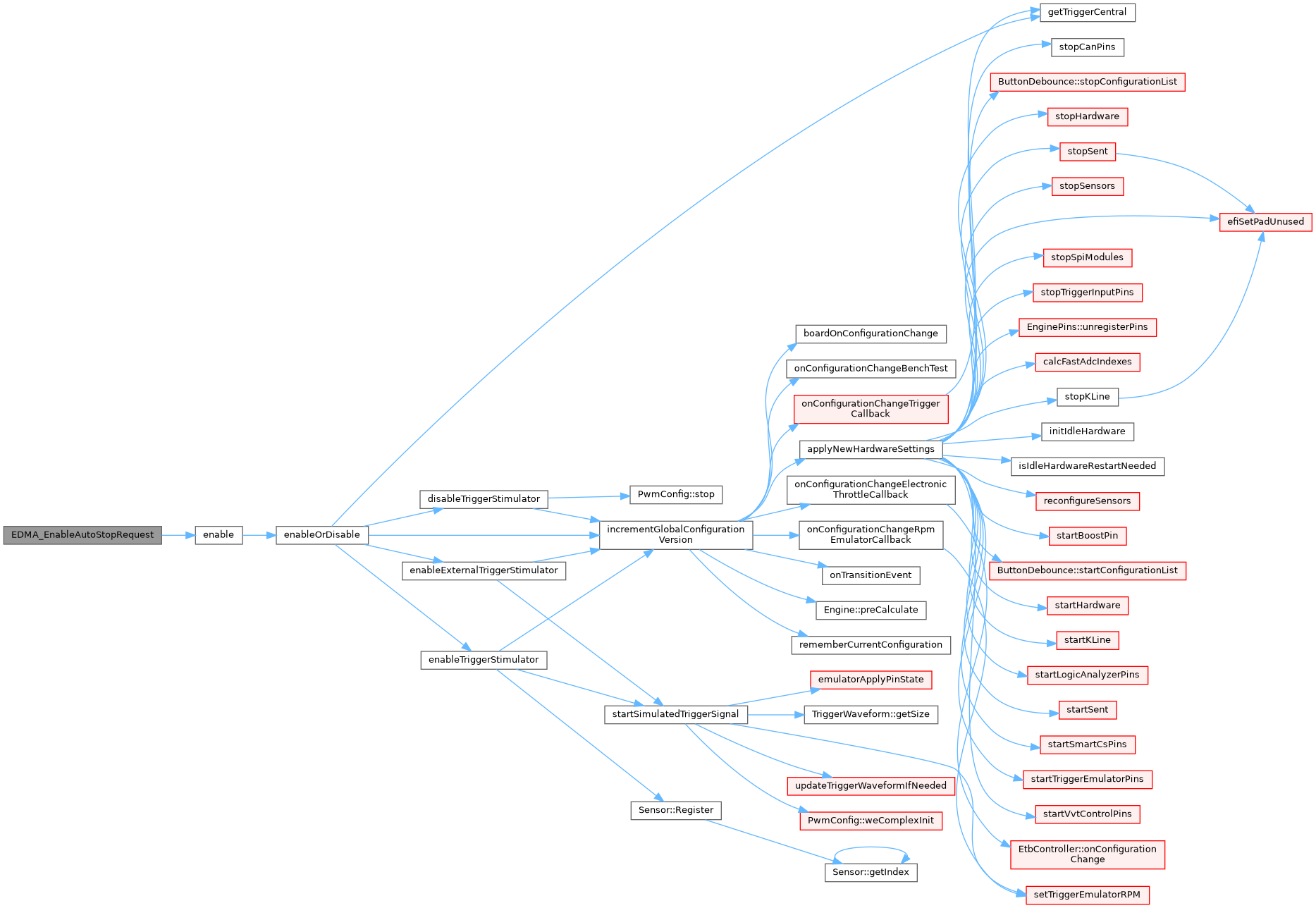

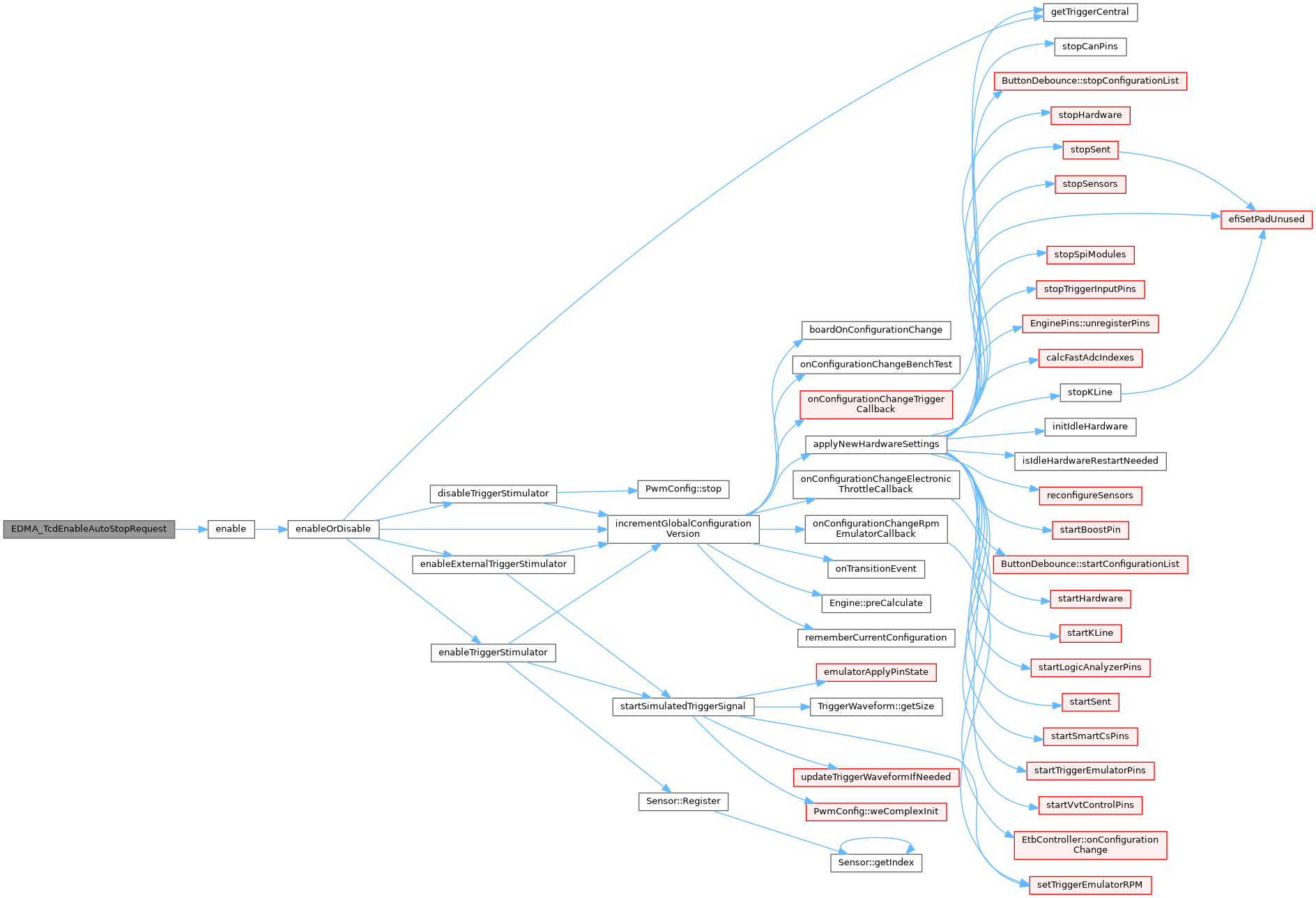

| static void | EDMA_EnableAutoStopRequest (DMA_Type *base, uint32_t channel, bool enable) |

| Enables an auto stop request for the eDMA transfer. | |

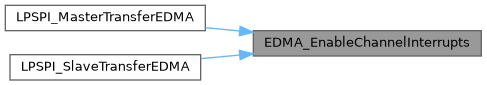

| void | EDMA_EnableChannelInterrupts (DMA_Type *base, uint32_t channel, uint32_t mask) |

| Enables the interrupt source for the eDMA transfer. | |

| void | EDMA_DisableChannelInterrupts (DMA_Type *base, uint32_t channel, uint32_t mask) |

| Disables the interrupt source for the eDMA transfer. | |

eDMA TCD Operation | |

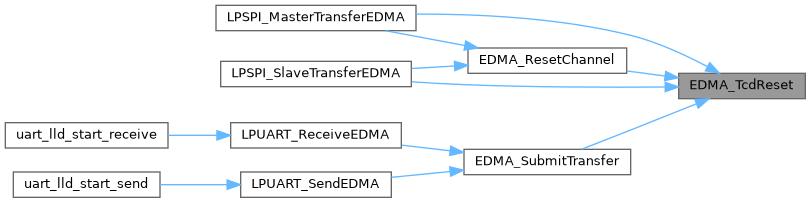

| void | EDMA_TcdReset (edma_tcd_t *tcd) |

| Sets all fields to default values for the TCD structure. | |

| void | EDMA_TcdSetTransferConfig (edma_tcd_t *tcd, const edma_transfer_config_t *config, edma_tcd_t *nextTcd) |

| Configures the eDMA TCD transfer attribute. | |

| void | EDMA_TcdSetMinorOffsetConfig (edma_tcd_t *tcd, const edma_minor_offset_config_t *config) |

| Configures the eDMA TCD minor offset feature. | |

| void | EDMA_TcdSetChannelLink (edma_tcd_t *tcd, edma_channel_link_type_t type, uint32_t linkedChannel) |

| Sets the channel link for the eDMA TCD. | |

| static void | EDMA_TcdSetBandWidth (edma_tcd_t *tcd, edma_bandwidth_t bandWidth) |

| Sets the bandwidth for the eDMA TCD. | |

| void | EDMA_TcdSetModulo (edma_tcd_t *tcd, edma_modulo_t srcModulo, edma_modulo_t destModulo) |

| Sets the source modulo and the destination modulo for the eDMA TCD. | |

| static void | EDMA_TcdEnableAutoStopRequest (edma_tcd_t *tcd, bool enable) |

| Sets the auto stop request for the eDMA TCD. | |

| void | EDMA_TcdEnableInterrupts (edma_tcd_t *tcd, uint32_t mask) |

| Enables the interrupt source for the eDMA TCD. | |

| void | EDMA_TcdDisableInterrupts (edma_tcd_t *tcd, uint32_t mask) |

| Disables the interrupt source for the eDMA TCD. | |

eDMA Channel Transfer Operation | |

| static void | EDMA_EnableChannelRequest (DMA_Type *base, uint32_t channel) |

| Enables the eDMA hardware channel request. | |

| static void | EDMA_DisableChannelRequest (DMA_Type *base, uint32_t channel) |

| Disables the eDMA hardware channel request. | |

| static void | EDMA_TriggerChannelStart (DMA_Type *base, uint32_t channel) |

| Starts the eDMA transfer by using the software trigger. | |

eDMA Channel Status Operation | |

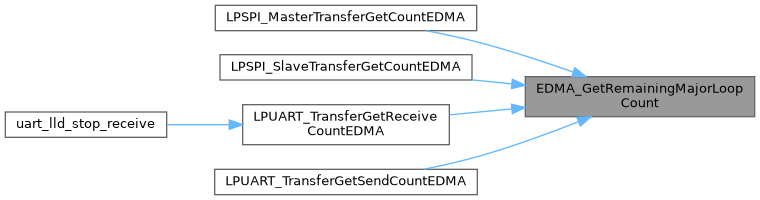

| uint32_t | EDMA_GetRemainingMajorLoopCount (DMA_Type *base, uint32_t channel) |

| Gets the remaining major loop count from the eDMA current channel TCD. | |

| static uint32_t | EDMA_GetErrorStatusFlags (DMA_Type *base) |

| Gets the eDMA channel error status flags. | |

| uint32_t | EDMA_GetChannelStatusFlags (DMA_Type *base, uint32_t channel) |

| Gets the eDMA channel status flags. | |

| void | EDMA_ClearChannelStatusFlags (DMA_Type *base, uint32_t channel, uint32_t mask) |

| Clears the eDMA channel status flags. | |

eDMA Transactional Operation | |

| void | EDMA_CreateHandle (edma_handle_t *handle, DMA_Type *base, uint32_t channel) |

| Creates the eDMA handle. | |

| void | EDMA_InstallTCDMemory (edma_handle_t *handle, edma_tcd_t *tcdPool, uint32_t tcdSize) |

| Installs the TCDs memory pool into the eDMA handle. | |

| void | EDMA_SetCallback (edma_handle_t *handle, edma_callback callback, void *userData) |

| Installs a callback function for the eDMA transfer. | |

| void | EDMA_PrepareTransfer (edma_transfer_config_t *config, void *srcAddr, uint32_t srcWidth, void *destAddr, uint32_t destWidth, uint32_t bytesEachRequest, uint32_t transferBytes, edma_transfer_type_t type) |

| Prepares the eDMA transfer structure. | |

| status_t | EDMA_SubmitTransfer (edma_handle_t *handle, const edma_transfer_config_t *config) |

| Submits the eDMA transfer request. | |

| void | EDMA_StartTransfer (edma_handle_t *handle) |

| eDMA starts transfer. | |

| void | EDMA_StopTransfer (edma_handle_t *handle) |

| eDMA stops transfer. | |

| void | EDMA_AbortTransfer (edma_handle_t *handle) |

| eDMA aborts transfer. | |

| static uint32_t | EDMA_GetUnusedTCDNumber (edma_handle_t *handle) |

| Get unused TCD slot number. | |

| static uint32_t | EDMA_GetNextTCDAddress (edma_handle_t *handle) |

| Get the next tcd address. | |

| void | EDMA_HandleIRQ (edma_handle_t *handle) |

| eDMA IRQ handler for the current major loop transfer completion. | |

Detailed Description

Typedef Documentation

◆ edma_bandwidth_t

| typedef enum _edma_bandwidth edma_bandwidth_t |

Bandwidth control.

◆ edma_callback

| typedef void(* edma_callback) (struct _edma_handle *handle, void *userData, bool transferDone, uint32_t tcds) |

Define callback function for eDMA.

This callback function is called in the EDMA interrupt handle. In normal mode, run into callback function means the transfer users need is done. In scatter gather mode, run into callback function means a transfer control block (tcd) is finished. Not all transfer finished, users can get the finished tcd numbers using interface EDMA_GetUnusedTCDNumber.

- Parameters

-

handle EDMA handle pointer, users shall not touch the values inside. userData The callback user parameter pointer. Users can use this parameter to involve things users need to change in EDMA callback function. transferDone If the current loaded transfer done. In normal mode it means if all transfer done. In scatter gather mode, this parameter shows is the current transfer block in EDMA register is done. As the load of core is different, it will be different if the new tcd loaded into EDMA registers while this callback called. If true, it always means new tcd still not loaded into registers, while false means new tcd already loaded into registers. tcds How many tcds are done from the last callback. This parameter only used in scatter gather mode. It tells user how many tcds are finished between the last callback and this.

Definition at line 242 of file fsl_edma.h.

◆ edma_channel_link_type_t

| typedef enum _edma_channel_link_type edma_channel_link_type_t |

Channel link type.

◆ edma_channel_Preemption_config_t

| typedef struct _edma_channel_Preemption_config edma_channel_Preemption_config_t |

eDMA channel priority configuration

◆ edma_config_t

| typedef struct _edma_config edma_config_t |

eDMA global configuration structure.

◆ edma_handle_t

| typedef struct _edma_handle edma_handle_t |

eDMA transfer handle structure

◆ edma_interrupt_enable_t

| typedef enum _edma_interrupt_enable edma_interrupt_enable_t |

eDMA interrupt source

◆ edma_minor_offset_config_t

| typedef struct _edma_minor_offset_config edma_minor_offset_config_t |

eDMA minor offset configuration

◆ edma_modulo_t

| typedef enum _edma_modulo edma_modulo_t |

eDMA modulo configuration

◆ edma_tcd_t

| typedef struct _edma_tcd edma_tcd_t |

eDMA TCD.

This structure is same as TCD register which is described in reference manual, and is used to configure the scatter/gather feature as a next hardware TCD.

◆ edma_transfer_config_t

| typedef struct _edma_transfer_config edma_transfer_config_t |

eDMA transfer configuration

This structure configures the source/destination transfer attribute.

◆ edma_transfer_size_t

| typedef enum _edma_transfer_size edma_transfer_size_t |

eDMA transfer configuration

◆ edma_transfer_type_t

| typedef enum _edma_transfer_type edma_transfer_type_t |

eDMA transfer type

Enumeration Type Documentation

◆ _edma_bandwidth

| enum _edma_bandwidth |

Bandwidth control.

Definition at line 84 of file fsl_edma.h.

◆ _edma_channel_link_type

Channel link type.

| Enumerator | |

|---|---|

| kEDMA_LinkNone | No channel link |

| kEDMA_MinorLink | Channel link after each minor loop |

| kEDMA_MajorLink | Channel link while major loop count exhausted |

Definition at line 92 of file fsl_edma.h.

◆ _edma_channel_status_flags

eDMA channel status flags.

Definition at line 100 of file fsl_edma.h.

◆ _edma_error_status_flags

eDMA channel error status flags.

Definition at line 108 of file fsl_edma.h.

◆ _edma_interrupt_enable

eDMA interrupt source

Definition at line 128 of file fsl_edma.h.

◆ _edma_modulo

| enum _edma_modulo |

eDMA modulo configuration

Definition at line 47 of file fsl_edma.h.

◆ _edma_transfer_size

| enum _edma_transfer_size |

eDMA transfer configuration

Definition at line 36 of file fsl_edma.h.

◆ _edma_transfer_status

eDMA transfer status

| Enumerator | |

|---|---|

| kStatus_EDMA_QueueFull | TCD queue is full. |

| kStatus_EDMA_Busy | Channel is busy and can't handle the transfer request. |

Definition at line 144 of file fsl_edma.h.

◆ _edma_transfer_type

| enum _edma_transfer_type |

eDMA transfer type

| Enumerator | |

|---|---|

| kEDMA_MemoryToMemory | Transfer from memory to memory |

| kEDMA_PeripheralToMemory | Transfer from peripheral to memory |

| kEDMA_MemoryToPeripheral | Transfer from memory to peripheral |

Definition at line 136 of file fsl_edma.h.

Function Documentation

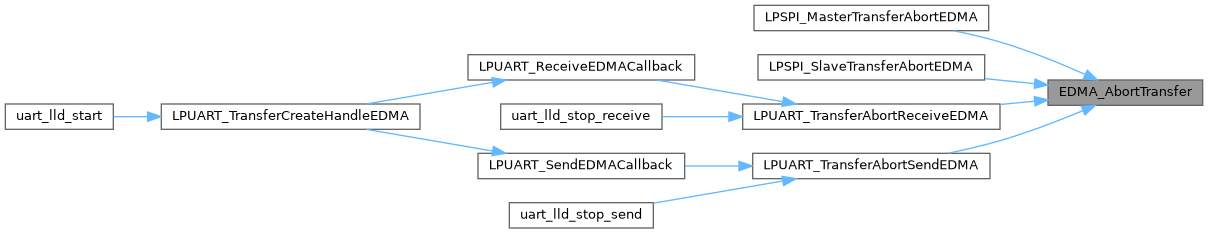

◆ EDMA_AbortTransfer()

| void EDMA_AbortTransfer | ( | edma_handle_t * | handle | ) |

eDMA aborts transfer.

This function disables the channel request and clear transfer status bits. Users can submit another transfer after calling this API.

- Parameters

-

handle DMA handle pointer.

brief eDMA aborts transfer.

This function disables the channel request and clear transfer status bits. Users can submit another transfer after calling this API.

param handle DMA handle pointer.

Definition at line 1164 of file fsl_edma.c.

Referenced by LPSPI_MasterTransferAbortEDMA(), LPSPI_SlaveTransferAbortEDMA(), LPUART_TransferAbortReceiveEDMA(), and LPUART_TransferAbortSendEDMA().

◆ EDMA_ClearChannelStatusFlags()

| void EDMA_ClearChannelStatusFlags | ( | DMA_Type * | base, |

| uint32_t | channel, | ||

| uint32_t | mask | ||

| ) |

Clears the eDMA channel status flags.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number. mask The mask of channel status to be cleared. Users need to use the defined _edma_channel_status_flags type.

brief Clears the eDMA channel status flags.

param base eDMA peripheral base address. param channel eDMA channel number. param mask The mask of channel status to be cleared. Users need to use the defined _edma_channel_status_flags type.

Definition at line 708 of file fsl_edma.c.

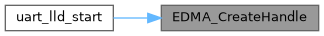

◆ EDMA_CreateHandle()

| void EDMA_CreateHandle | ( | edma_handle_t * | handle, |

| DMA_Type * | base, | ||

| uint32_t | channel | ||

| ) |

Creates the eDMA handle.

This function is called if using the transactional API for eDMA. This function initializes the internal state of the eDMA handle.

- Parameters

-

handle eDMA handle pointer. The eDMA handle stores callback function and parameters. base eDMA peripheral base address. channel eDMA channel number.

brief Creates the eDMA handle.

This function is called if using the transactional API for eDMA. This function initializes the internal state of the eDMA handle.

param handle eDMA handle pointer. The eDMA handle stores callback function and parameters. param base eDMA peripheral base address. param channel eDMA channel number.

Definition at line 757 of file fsl_edma.c.

Referenced by uart_lld_start().

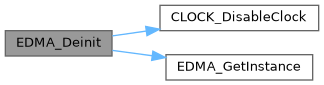

◆ EDMA_Deinit()

| void EDMA_Deinit | ( | DMA_Type * | base | ) |

Deinitializes the eDMA peripheral.

This function gates the eDMA clock.

- Parameters

-

base eDMA peripheral base address.

brief Deinitializes the eDMA peripheral.

This function gates the eDMA clock.

param base eDMA peripheral base address.

Definition at line 143 of file fsl_edma.c.

◆ EDMA_DisableChannelInterrupts()

| void EDMA_DisableChannelInterrupts | ( | DMA_Type * | base, |

| uint32_t | channel, | ||

| uint32_t | mask | ||

| ) |

Disables the interrupt source for the eDMA transfer.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number. mask The mask of the interrupt source to be set. Use the defined edma_interrupt_enable_t type.

brief Disables the interrupt source for the eDMA transfer.

param base eDMA peripheral base address. param channel eDMA channel number. param mask The mask of the interrupt source to be set. Use the defined edma_interrupt_enable_t type.

Definition at line 361 of file fsl_edma.c.

◆ EDMA_DisableChannelRequest()

|

inlinestatic |

Disables the eDMA hardware channel request.

This function disables the hardware channel request.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number.

Definition at line 669 of file fsl_edma.h.

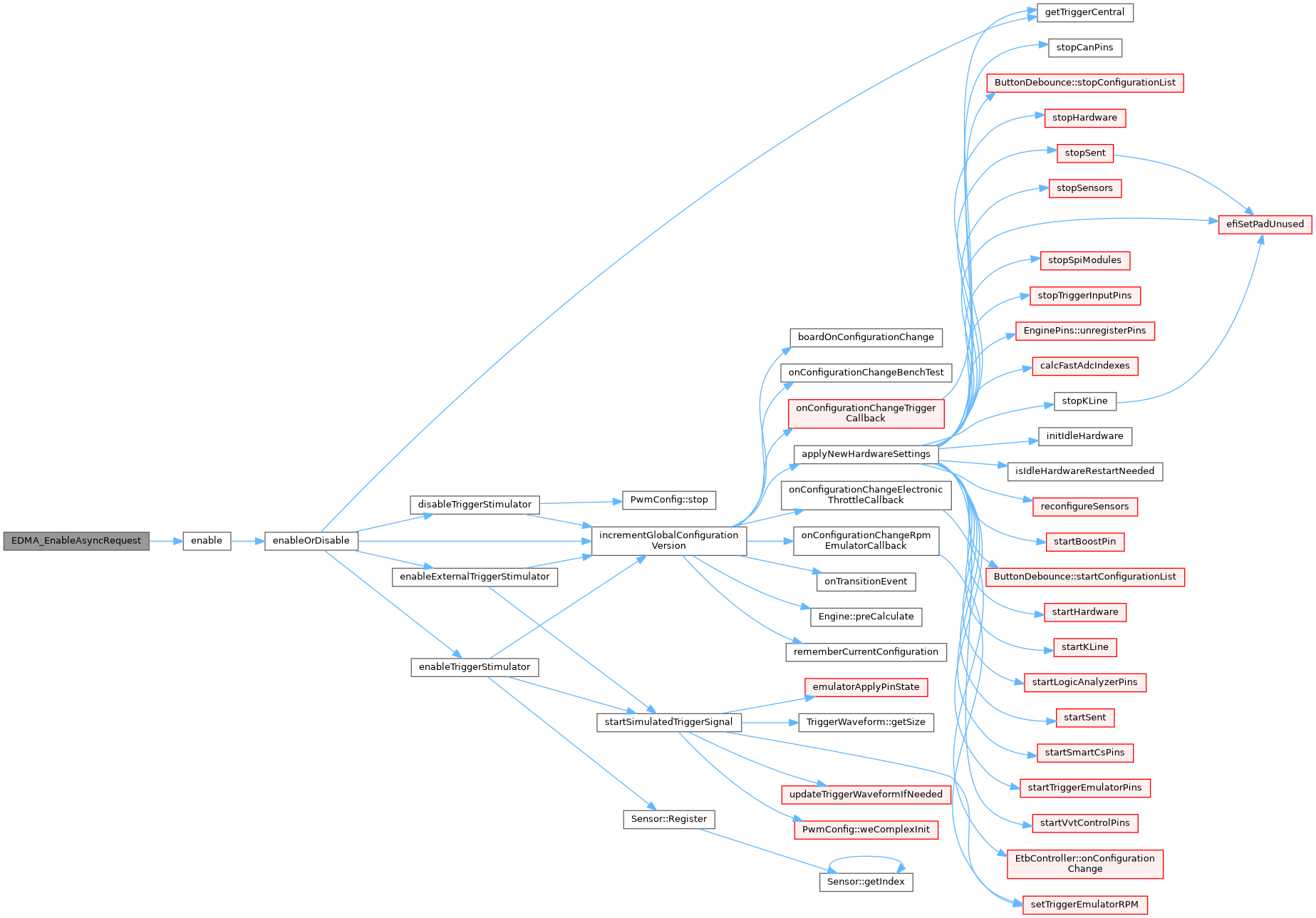

◆ EDMA_EnableAsyncRequest()

|

inlinestatic |

Enables an async request for the eDMA transfer.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number. enable The command to enable (true) or disable (false).

Definition at line 456 of file fsl_edma.h.

◆ EDMA_EnableAutoStopRequest()

|

inlinestatic |

Enables an auto stop request for the eDMA transfer.

If enabling the auto stop request, the eDMA hardware automatically disables the hardware channel request.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number. enable The command to enable (true) or disable (false).

Definition at line 473 of file fsl_edma.h.

◆ EDMA_EnableChannelInterrupts()

| void EDMA_EnableChannelInterrupts | ( | DMA_Type * | base, |

| uint32_t | channel, | ||

| uint32_t | mask | ||

| ) |

Enables the interrupt source for the eDMA transfer.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number. mask The mask of interrupt source to be set. Users need to use the defined edma_interrupt_enable_t type.

brief Enables the interrupt source for the eDMA transfer.

param base eDMA peripheral base address. param channel eDMA channel number. param mask The mask of interrupt source to be set. Users need to use the defined edma_interrupt_enable_t type.

Definition at line 330 of file fsl_edma.c.

Referenced by LPSPI_MasterTransferEDMA(), and LPSPI_SlaveTransferEDMA().

◆ EDMA_EnableChannelRequest()

|

inlinestatic |

Enables the eDMA hardware channel request.

This function enables the hardware channel request.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number.

Definition at line 654 of file fsl_edma.h.

◆ EDMA_GetChannelStatusFlags()

| uint32_t EDMA_GetChannelStatusFlags | ( | DMA_Type * | base, |

| uint32_t | channel | ||

| ) |

Gets the eDMA channel status flags.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number.

- Returns

- The mask of channel status flags. Users need to use the _edma_channel_status_flags type to decode the return variables.

brief Gets the eDMA channel status flags.

param base eDMA peripheral base address. param channel eDMA channel number. return The mask of channel status flags. Users need to use the _edma_channel_status_flags type to decode the return variables.

Definition at line 684 of file fsl_edma.c.

Referenced by DMA0_04_DriverIRQHandler(), DMA0_08_DriverIRQHandler(), DMA0_0_4_DriverIRQHandler(), DMA0_10_14_DriverIRQHandler(), DMA0_11_15_DriverIRQHandler(), DMA0_15_DriverIRQHandler(), DMA0_16_20_DriverIRQHandler(), DMA0_17_21_DriverIRQHandler(), DMA0_18_22_DriverIRQHandler(), DMA0_19_23_DriverIRQHandler(), DMA0_19_DriverIRQHandler(), DMA0_1_5_DriverIRQHandler(), DMA0_210_DriverIRQHandler(), DMA0_24_28_DriverIRQHandler(), DMA0_25_29_DriverIRQHandler(), DMA0_26_30_DriverIRQHandler(), DMA0_26_DriverIRQHandler(), DMA0_27_31_DriverIRQHandler(), DMA0_2_6_DriverIRQHandler(), DMA0_311_DriverIRQHandler(), DMA0_37_DriverIRQHandler(), DMA0_3_7_DriverIRQHandler(), DMA0_412_DriverIRQHandler(), DMA0_513_DriverIRQHandler(), DMA0_614_DriverIRQHandler(), DMA0_715_DriverIRQHandler(), DMA0_8_12_DriverIRQHandler(), DMA0_9_13_DriverIRQHandler(), DMA0_DMA16_DriverIRQHandler(), DMA10_DMA26_DriverIRQHandler(), DMA11_DMA27_DriverIRQHandler(), DMA12_DMA28_DriverIRQHandler(), DMA13_DMA29_DriverIRQHandler(), DMA14_DMA30_DriverIRQHandler(), DMA15_DMA31_DriverIRQHandler(), DMA1_04_DriverIRQHandler(), DMA1_08_DriverIRQHandler(), DMA1_15_DriverIRQHandler(), DMA1_19_DriverIRQHandler(), DMA1_210_DriverIRQHandler(), DMA1_26_DriverIRQHandler(), DMA1_311_DriverIRQHandler(), DMA1_37_DriverIRQHandler(), DMA1_412_DriverIRQHandler(), DMA1_513_DriverIRQHandler(), DMA1_614_DriverIRQHandler(), DMA1_715_DriverIRQHandler(), DMA1_DMA17_DriverIRQHandler(), DMA2_DMA18_DriverIRQHandler(), DMA3_DMA19_DriverIRQHandler(), DMA4_DMA20_DriverIRQHandler(), DMA5_DMA21_DriverIRQHandler(), DMA6_DMA22_DriverIRQHandler(), DMA7_DMA23_DriverIRQHandler(), DMA8_DMA24_DriverIRQHandler(), and DMA9_DMA25_DriverIRQHandler().

◆ EDMA_GetDefaultConfig()

| void EDMA_GetDefaultConfig | ( | edma_config_t * | config | ) |

Gets the eDMA default configuration structure.

This function sets the configuration structure to default values. The default configuration is set to the following values.

- Parameters

-

config A pointer to the eDMA configuration structure.

brief Gets the eDMA default configuration structure.

This function sets the configuration structure to default values. The default configuration is set to the following values. code config.enableContinuousLinkMode = false; config.enableHaltOnError = true; config.enableRoundRobinArbitration = false; config.enableDebugMode = false; endcode

param config A pointer to the eDMA configuration structure.

Definition at line 165 of file fsl_edma.c.

Referenced by dmaInit().

◆ EDMA_GetErrorStatusFlags()

|

inlinestatic |

Gets the eDMA channel error status flags.

- Parameters

-

base eDMA peripheral base address.

- Returns

- The mask of error status flags. Users need to use the _edma_error_status_flags type to decode the return variables.

Definition at line 727 of file fsl_edma.h.

◆ EDMA_GetNextTCDAddress()

|

inlinestatic |

Get the next tcd address.

This function gets the next tcd address. If this is last TCD, return 0.

- Parameters

-

handle DMA handle pointer.

- Returns

- The next TCD address.

Definition at line 888 of file fsl_edma.h.

◆ EDMA_GetRemainingMajorLoopCount()

| uint32_t EDMA_GetRemainingMajorLoopCount | ( | DMA_Type * | base, |

| uint32_t | channel | ||

| ) |

Gets the remaining major loop count from the eDMA current channel TCD.

This function checks the TCD (Task Control Descriptor) status for a specified eDMA channel and returns the number of major loop count that has not finished.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number.

- Returns

- Major loop count which has not been transferred yet for the current TCD.

- Note

- 1. This function can only be used to get unfinished major loop count of transfer without the next TCD, or it might be inaccuracy.

- The unfinished/remaining transfer bytes cannot be obtained directly from registers while the channel is running. Because to calculate the remaining bytes, the initial NBYTES configured in DMA_TCDn_NBYTES_MLNO register is needed while the eDMA IP does not support getting it while a channel is active. In another word, the NBYTES value reading is always the actual (decrementing) NBYTES value the dma_engine is working with while a channel is running. Consequently, to get the remaining transfer bytes, a software-saved initial value of NBYTES (for example copied before enabling the channel) is needed. The formula to calculate it is shown below: RemainingBytes = RemainingMajorLoopCount * NBYTES(initially configured)

brief Gets the remaining major loop count from the eDMA current channel TCD.

This function checks the TCD (Task Control Descriptor) status for a specified eDMA channel and returns the number of major loop count that has not finished.

param base eDMA peripheral base address. param channel eDMA channel number. return Major loop count which has not been transferred yet for the current TCD. note 1. This function can only be used to get unfinished major loop count of transfer without the next TCD, or it might be inaccuracy.

- The unfinished/remaining transfer bytes cannot be obtained directly from registers while the channel is running. Because to calculate the remaining bytes, the initial NBYTES configured in DMA_TCDn_NBYTES_MLNO register is needed while the eDMA IP does not support getting it while a channel is active. In another word, the NBYTES value reading is always the actual (decrementing) NBYTES value the dma_engine is working with while a channel is running. Consequently, to get the remaining transfer bytes, a software-saved initial value of NBYTES (for example copied before enabling the channel) is needed. The formula to calculate it is shown below: RemainingBytes = RemainingMajorLoopCount * NBYTES(initially configured)

Definition at line 648 of file fsl_edma.c.

Referenced by LPSPI_MasterTransferGetCountEDMA(), LPSPI_SlaveTransferGetCountEDMA(), LPUART_TransferGetReceiveCountEDMA(), and LPUART_TransferGetSendCountEDMA().

◆ EDMA_GetUnusedTCDNumber()

|

inlinestatic |

Get unused TCD slot number.

This function gets current tcd index which is run. If the TCD pool pointer is NULL, it will return 0.

- Parameters

-

handle DMA handle pointer.

- Returns

- The unused tcd slot number.

Definition at line 875 of file fsl_edma.h.

◆ EDMA_HandleIRQ()

| void EDMA_HandleIRQ | ( | edma_handle_t * | handle | ) |

eDMA IRQ handler for the current major loop transfer completion.

This function clears the channel major interrupt flag and calls the callback function if it is not NULL.

Note: For the case using TCD queue, when the major iteration count is exhausted, additional operations are performed. These include the final address adjustments and reloading of the BITER field into the CITER. Assertion of an optional interrupt request also occurs at this time, as does a possible fetch of a new TCD from memory using the scatter/gather address pointer included in the descriptor (if scatter/gather is enabled).

For instance, when the time interrupt of TCD[0] happens, the TCD[1] has already been loaded into the eDMA engine. As sga and sga_index are calculated based on the DLAST_SGA bitfield lies in the TCD_CSR register, the sga_index in this case should be 2 (DLAST_SGA of TCD[1] stores the address of TCD[2]). Thus, the "tcdUsed" updated should be (tcdUsed - 2U) which indicates the number of TCDs can be loaded in the memory pool (because TCD[0] and TCD[1] have been loaded into the eDMA engine at this point already.).

For the last two continuous ISRs in a scatter/gather process, they both load the last TCD (The last ISR does not load a new TCD) from the memory pool to the eDMA engine when major loop completes. Therefore, ensure that the header and tcdUsed updated are identical for them. tcdUsed are both 0 in this case as no TCD to be loaded.

See the "eDMA basic data flow" in the eDMA Functional description section of the Reference Manual for further details.

- Parameters

-

handle eDMA handle pointer.

brief eDMA IRQ handler for the current major loop transfer completion.

This function clears the channel major interrupt flag and calls the callback function if it is not NULL.

Note: For the case using TCD queue, when the major iteration count is exhausted, additional operations are performed. These include the final address adjustments and reloading of the BITER field into the CITER. Assertion of an optional interrupt request also occurs at this time, as does a possible fetch of a new TCD from memory using the scatter/gather address pointer included in the descriptor (if scatter/gather is enabled).

For instance, when the time interrupt of TCD[0] happens, the TCD[1] has already been loaded into the eDMA engine. As sga and sga_index are calculated based on the DLAST_SGA bitfield lies in the TCD_CSR register, the sga_index in this case should be 2 (DLAST_SGA of TCD[1] stores the address of TCD[2]). Thus, the "tcdUsed" updated should be (tcdUsed - 2U) which indicates the number of TCDs can be loaded in the memory pool (because TCD[0] and TCD[1] have been loaded into the eDMA engine at this point already.).

For the last two continuous ISRs in a scatter/gather process, they both load the last TCD (The last ISR does not load a new TCD) from the memory pool to the eDMA engine when major loop completes. Therefore, ensure that the header and tcdUsed updated are identical for them. tcdUsed are both 0 in this case as no TCD to be loaded.

See the "eDMA basic data flow" in the eDMA Functional description section of the Reference Manual for further details.

param handle eDMA handle pointer.

Definition at line 1213 of file fsl_edma.c.

Referenced by DMA0_04_DriverIRQHandler(), DMA0_08_DriverIRQHandler(), DMA0_0_4_DriverIRQHandler(), DMA0_10_14_DriverIRQHandler(), DMA0_11_15_DriverIRQHandler(), DMA0_15_DriverIRQHandler(), DMA0_16_20_DriverIRQHandler(), DMA0_17_21_DriverIRQHandler(), DMA0_18_22_DriverIRQHandler(), DMA0_19_23_DriverIRQHandler(), DMA0_19_DriverIRQHandler(), DMA0_1_5_DriverIRQHandler(), DMA0_210_DriverIRQHandler(), DMA0_24_28_DriverIRQHandler(), DMA0_25_29_DriverIRQHandler(), DMA0_26_30_DriverIRQHandler(), DMA0_26_DriverIRQHandler(), DMA0_27_31_DriverIRQHandler(), DMA0_2_6_DriverIRQHandler(), DMA0_311_DriverIRQHandler(), DMA0_37_DriverIRQHandler(), DMA0_3_7_DriverIRQHandler(), DMA0_412_DriverIRQHandler(), DMA0_513_DriverIRQHandler(), DMA0_614_DriverIRQHandler(), DMA0_715_DriverIRQHandler(), DMA0_8_12_DriverIRQHandler(), DMA0_9_13_DriverIRQHandler(), DMA0_DMA16_DriverIRQHandler(), DMA0_DriverIRQHandler(), DMA10_DMA26_DriverIRQHandler(), DMA10_DriverIRQHandler(), DMA11_DMA27_DriverIRQHandler(), DMA11_DriverIRQHandler(), DMA12_DMA28_DriverIRQHandler(), DMA12_DriverIRQHandler(), DMA13_DMA29_DriverIRQHandler(), DMA13_DriverIRQHandler(), DMA14_DMA30_DriverIRQHandler(), DMA14_DriverIRQHandler(), DMA15_DMA31_DriverIRQHandler(), DMA15_DriverIRQHandler(), DMA16_DriverIRQHandler(), DMA17_DriverIRQHandler(), DMA18_DriverIRQHandler(), DMA19_DriverIRQHandler(), DMA1_04_DriverIRQHandler(), DMA1_08_DriverIRQHandler(), DMA1_15_DriverIRQHandler(), DMA1_19_DriverIRQHandler(), DMA1_210_DriverIRQHandler(), DMA1_26_DriverIRQHandler(), DMA1_311_DriverIRQHandler(), DMA1_37_DriverIRQHandler(), DMA1_412_DriverIRQHandler(), DMA1_513_DriverIRQHandler(), DMA1_614_DriverIRQHandler(), DMA1_715_DriverIRQHandler(), DMA1_DMA17_DriverIRQHandler(), DMA1_DriverIRQHandler(), DMA20_DriverIRQHandler(), DMA21_DriverIRQHandler(), DMA22_DriverIRQHandler(), DMA23_DriverIRQHandler(), DMA24_DriverIRQHandler(), DMA25_DriverIRQHandler(), DMA26_DriverIRQHandler(), DMA27_DriverIRQHandler(), DMA28_DriverIRQHandler(), DMA29_DriverIRQHandler(), DMA2_DMA18_DriverIRQHandler(), DMA2_DriverIRQHandler(), DMA30_DriverIRQHandler(), DMA31_DriverIRQHandler(), DMA3_DMA19_DriverIRQHandler(), DMA3_DriverIRQHandler(), DMA4_DMA20_DriverIRQHandler(), DMA4_DriverIRQHandler(), DMA5_DMA21_DriverIRQHandler(), DMA5_DriverIRQHandler(), DMA6_DMA22_DriverIRQHandler(), DMA6_DriverIRQHandler(), DMA7_DMA23_DriverIRQHandler(), DMA7_DriverIRQHandler(), DMA8_DMA24_DriverIRQHandler(), DMA8_DriverIRQHandler(), DMA9_DMA25_DriverIRQHandler(), and DMA9_DriverIRQHandler().

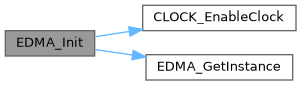

◆ EDMA_Init()

| void EDMA_Init | ( | DMA_Type * | base, |

| const edma_config_t * | config | ||

| ) |

Initializes the eDMA peripheral.

This function ungates the eDMA clock and configures the eDMA peripheral according to the configuration structure.

- Parameters

-

base eDMA peripheral base address. config A pointer to the configuration structure, see "edma_config_t".

- Note

- This function enables the minor loop map feature.

brief Initializes the eDMA peripheral.

This function ungates the eDMA clock and configures the eDMA peripheral according to the configuration structure.

param base eDMA peripheral base address. param config A pointer to the configuration structure, see "edma_config_t". note This function enables the minor loop map feature.

Definition at line 113 of file fsl_edma.c.

Referenced by dmaInit().

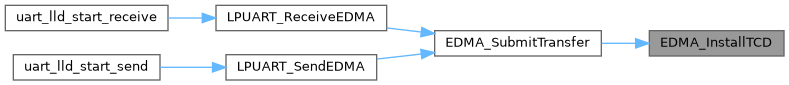

◆ EDMA_InstallTCD()

| void EDMA_InstallTCD | ( | DMA_Type * | base, |

| uint32_t | channel, | ||

| edma_tcd_t * | tcd | ||

| ) |

Push content of TCD structure into hardware TCD register.

- Parameters

-

base EDMA peripheral base address. channel EDMA channel number. tcd Point to TCD structure.

brief Push content of TCD structure into hardware TCD register.

param base EDMA peripheral base address. param channel EDMA channel number. param tcd Point to TCD structure.

Definition at line 81 of file fsl_edma.c.

Referenced by EDMA_SubmitTransfer().

◆ EDMA_InstallTCDMemory()

| void EDMA_InstallTCDMemory | ( | edma_handle_t * | handle, |

| edma_tcd_t * | tcdPool, | ||

| uint32_t | tcdSize | ||

| ) |

Installs the TCDs memory pool into the eDMA handle.

This function is called after the EDMA_CreateHandle to use scatter/gather feature. This function shall only be used while users need to use scatter gather mode. Scatter gather mode enables EDMA to load a new transfer control block (tcd) in hardware, and automatically reconfigure that DMA channel for a new transfer. Users need to prepare tcd memory and also configure tcds using interface EDMA_SubmitTransfer.

- Parameters

-

handle eDMA handle pointer. tcdPool A memory pool to store TCDs. It must be 32 bytes aligned. tcdSize The number of TCD slots.

brief Installs the TCDs memory pool into the eDMA handle.

This function is called after the EDMA_CreateHandle to use scatter/gather feature. This function shall only be used while users need to use scatter gather mode. Scatter gather mode enables EDMA to load a new transfer control block (tcd) in hardware, and automatically reconfigure that DMA channel for a new transfer. Users need to prepare tcd memory and also configure tcds using interface EDMA_SubmitTransfer.

param handle eDMA handle pointer. param tcdPool A memory pool to store TCDs. It must be 32 bytes aligned. param tcdSize The number of TCD slots.

Definition at line 812 of file fsl_edma.c.

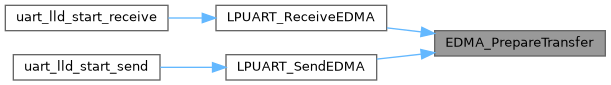

◆ EDMA_PrepareTransfer()

| void EDMA_PrepareTransfer | ( | edma_transfer_config_t * | config, |

| void * | srcAddr, | ||

| uint32_t | srcWidth, | ||

| void * | destAddr, | ||

| uint32_t | destWidth, | ||

| uint32_t | bytesEachRequest, | ||

| uint32_t | transferBytes, | ||

| edma_transfer_type_t | type | ||

| ) |

Prepares the eDMA transfer structure.

This function prepares the transfer configuration structure according to the user input.

- Parameters

-

config The user configuration structure of type edma_transfer_t. srcAddr eDMA transfer source address. srcWidth eDMA transfer source address width(bytes). destAddr eDMA transfer destination address. destWidth eDMA transfer destination address width(bytes). bytesEachRequest eDMA transfer bytes per channel request. transferBytes eDMA transfer bytes to be transferred. type eDMA transfer type.

- Note

- The data address and the data width must be consistent. For example, if the SRC is 4 bytes, the source address must be 4 bytes aligned, or it results in source address error (SAE).

brief Prepares the eDMA transfer structure.

This function prepares the transfer configuration structure according to the user input.

param config The user configuration structure of type edma_transfer_t. param srcAddr eDMA transfer source address. param srcWidth eDMA transfer source address width(bytes). param destAddr eDMA transfer destination address. param destWidth eDMA transfer destination address width(bytes). param bytesEachRequest eDMA transfer bytes per channel request. param transferBytes eDMA transfer bytes to be transferred. param type eDMA transfer type. note The data address and the data width must be consistent. For example, if the SRC is 4 bytes, the source address must be 4 bytes aligned, or it results in source address error (SAE).

Definition at line 861 of file fsl_edma.c.

Referenced by LPUART_ReceiveEDMA(), and LPUART_SendEDMA().

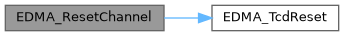

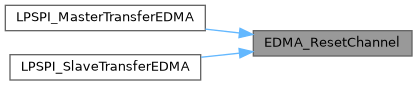

◆ EDMA_ResetChannel()

| void EDMA_ResetChannel | ( | DMA_Type * | base, |

| uint32_t | channel | ||

| ) |

Sets all TCD registers to default values.

This function sets TCD registers for this channel to default values.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number.

- Note

- This function must not be called while the channel transfer is ongoing or it causes unpredictable results.

- This function enables the auto stop request feature.

brief Sets all TCD registers to default values.

This function sets TCD registers for this channel to default values.

param base eDMA peripheral base address. param channel eDMA channel number. note This function must not be called while the channel transfer is ongoing or it causes unpredictable results. note This function enables the auto stop request feature.

Definition at line 189 of file fsl_edma.c.

Referenced by LPSPI_MasterTransferEDMA(), and LPSPI_SlaveTransferEDMA().

◆ EDMA_SetBandWidth()

| void EDMA_SetBandWidth | ( | DMA_Type * | base, |

| uint32_t | channel, | ||

| edma_bandwidth_t | bandWidth | ||

| ) |

Sets the bandwidth for the eDMA transfer.

Because the eDMA processes the minor loop, it continuously generates read/write sequences until the minor count is exhausted. The bandwidth forces the eDMA to stall after the completion of each read/write access to control the bus request bandwidth seen by the crossbar switch.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number. bandWidth A bandwidth setting, which can be one of the following: - kEDMABandwidthStallNone

- kEDMABandwidthStall4Cycle

- kEDMABandwidthStall8Cycle

Because the eDMA processes the minor loop, it continuously generates read/write sequences until the minor count is exhausted. The bandwidth forces the eDMA to stall after the completion of each read/write access to control the bus request bandwidth seen by the crossbar switch.

param base eDMA peripheral base address. param channel eDMA channel number. param bandWidth A bandwidth setting, which can be one of the following: arg kEDMABandwidthStallNone arg kEDMABandwidthStall4Cycle arg kEDMABandwidthStall8Cycle

Definition at line 293 of file fsl_edma.c.

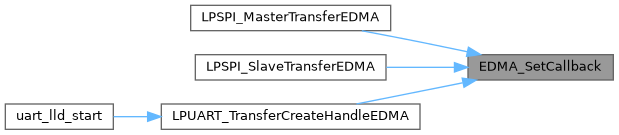

◆ EDMA_SetCallback()

| void EDMA_SetCallback | ( | edma_handle_t * | handle, |

| edma_callback | callback, | ||

| void * | userData | ||

| ) |

Installs a callback function for the eDMA transfer.

This callback is called in the eDMA IRQ handler. Use the callback to do something after the current major loop transfer completes. This function will be called every time one tcd finished transfer.

- Parameters

-

handle eDMA handle pointer. callback eDMA callback function pointer. userData A parameter for the callback function.

brief Installs a callback function for the eDMA transfer.

This callback is called in the eDMA IRQ handler. Use the callback to do something after the current major loop transfer completes. This function will be called every time one tcd finished transfer.

param handle eDMA handle pointer. param callback eDMA callback function pointer. param userData A parameter for the callback function.

Definition at line 836 of file fsl_edma.c.

Referenced by LPSPI_MasterTransferEDMA(), LPSPI_SlaveTransferEDMA(), and LPUART_TransferCreateHandleEDMA().

◆ EDMA_SetChannelLink()

| void EDMA_SetChannelLink | ( | DMA_Type * | base, |

| uint32_t | channel, | ||

| edma_channel_link_type_t | type, | ||

| uint32_t | linkedChannel | ||

| ) |

Sets the channel link for the eDMA transfer.

This function configures either the minor link or the major link mode. The minor link means that the channel link is triggered every time CITER decreases by 1. The major link means that the channel link is triggered when the CITER is exhausted.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number. type A channel link type, which can be one of the following: - kEDMA_LinkNone

- kEDMA_MinorLink

- kEDMA_MajorLink

linkedChannel The linked channel number.

- Note

- Users should ensure that DONE flag is cleared before calling this interface, or the configuration is invalid.

brief Sets the channel link for the eDMA transfer.

This function configures either the minor link or the major link mode. The minor link means that the channel link is triggered every time CITER decreases by 1. The major link means that the channel link is triggered when the CITER is exhausted.

param base eDMA peripheral base address. param channel eDMA channel number. param type A channel link type, which can be one of the following: arg kEDMA_LinkNone arg kEDMA_MinorLink arg kEDMA_MajorLink param linkedChannel The linked channel number. note Users should ensure that DONE flag is cleared before calling this interface, or the configuration is invalid.

Definition at line 271 of file fsl_edma.c.

◆ EDMA_SetChannelPreemptionConfig()

|

inlinestatic |

Configures the eDMA channel preemption feature.

This function configures the channel preemption attribute and the priority of the channel.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number config A pointer to the channel preemption configuration structure.

Definition at line 388 of file fsl_edma.h.

◆ EDMA_SetMinorOffsetConfig()

| void EDMA_SetMinorOffsetConfig | ( | DMA_Type * | base, |

| uint32_t | channel, | ||

| const edma_minor_offset_config_t * | config | ||

| ) |

Configures the eDMA minor offset feature.

The minor offset means that the signed-extended value is added to the source address or destination address after each minor loop.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number. config A pointer to the minor offset configuration structure.

brief Configures the eDMA minor offset feature.

The minor offset means that the signed-extended value is added to the source address or destination address after each minor loop.

param base eDMA peripheral base address. param channel eDMA channel number. param config A pointer to the minor offset configuration structure.

Definition at line 240 of file fsl_edma.c.

◆ EDMA_SetModulo()

| void EDMA_SetModulo | ( | DMA_Type * | base, |

| uint32_t | channel, | ||

| edma_modulo_t | srcModulo, | ||

| edma_modulo_t | destModulo | ||

| ) |

Sets the source modulo and the destination modulo for the eDMA transfer.

This function defines a specific address range specified to be the value after (SADDR + SOFF)/(DADDR + DOFF) calculation is performed or the original register value. It provides the ability to implement a circular data queue easily.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number. srcModulo A source modulo value. destModulo A destination modulo value.

brief Sets the source modulo and the destination modulo for the eDMA transfer.

This function defines a specific address range specified to be the value after (SADDR + SOFF)/(DADDR + DOFF) calculation is performed or the original register value. It provides the ability to implement a circular data queue easily.

param base eDMA peripheral base address. param channel eDMA channel number. param srcModulo A source modulo value. param destModulo A destination modulo value.

Definition at line 312 of file fsl_edma.c.

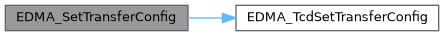

◆ EDMA_SetTransferConfig()

| void EDMA_SetTransferConfig | ( | DMA_Type * | base, |

| uint32_t | channel, | ||

| const edma_transfer_config_t * | config, | ||

| edma_tcd_t * | nextTcd | ||

| ) |

Configures the eDMA transfer attribute.

This function configures the transfer attribute, including source address, destination address, transfer size, address offset, and so on. It also configures the scatter gather feature if the user supplies the TCD address. Example:

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number. config Pointer to eDMA transfer configuration structure. nextTcd Point to TCD structure. It can be NULL if users do not want to enable scatter/gather feature.

- Note

- If nextTcd is not NULL, it means scatter gather feature is enabled and DREQ bit is cleared in the previous transfer configuration, which is set in the eDMA_ResetChannel.

brief Configures the eDMA transfer attribute.

This function configures the transfer attribute, including source address, destination address, transfer size, address offset, and so on. It also configures the scatter gather feature if the user supplies the TCD address. Example: code edma_transfer_t config; edma_tcd_t tcd; config.srcAddr = ..; config.destAddr = ..; ... EDMA_SetTransferConfig(DMA0, channel, &config, &stcd); endcode

param base eDMA peripheral base address. param channel eDMA channel number. param config Pointer to eDMA transfer configuration structure. param nextTcd Point to TCD structure. It can be NULL if users do not want to enable scatter/gather feature. note If nextTcd is not NULL, it means scatter gather feature is enabled and DREQ bit is cleared in the previous transfer configuration, which is set in the eDMA_ResetChannel.

Definition at line 221 of file fsl_edma.c.

Referenced by EDMA_SubmitTransfer(), LPSPI_MasterTransferEDMA(), and LPSPI_SlaveTransferEDMA().

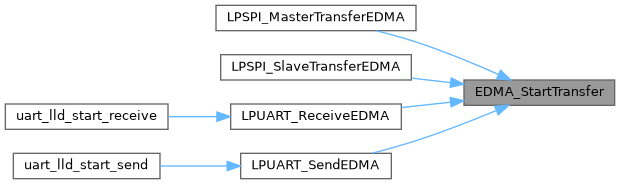

◆ EDMA_StartTransfer()

| void EDMA_StartTransfer | ( | edma_handle_t * | handle | ) |

eDMA starts transfer.

This function enables the channel request. Users can call this function after submitting the transfer request or before submitting the transfer request.

- Parameters

-

handle eDMA handle pointer.

brief eDMA starts transfer.

This function enables the channel request. Users can call this function after submitting the transfer request or before submitting the transfer request.

param handle eDMA handle pointer.

Definition at line 1103 of file fsl_edma.c.

Referenced by LPSPI_MasterTransferEDMA(), LPSPI_SlaveTransferEDMA(), LPUART_ReceiveEDMA(), and LPUART_SendEDMA().

◆ EDMA_StopTransfer()

| void EDMA_StopTransfer | ( | edma_handle_t * | handle | ) |

eDMA stops transfer.

This function disables the channel request to pause the transfer. Users can call EDMA_StartTransfer() again to resume the transfer.

- Parameters

-

handle eDMA handle pointer.

brief eDMA stops transfer.

This function disables the channel request to pause the transfer. Users can call EDMA_StartTransfer() again to resume the transfer.

param handle eDMA handle pointer.

Definition at line 1148 of file fsl_edma.c.

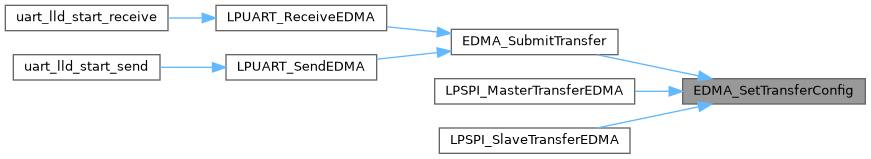

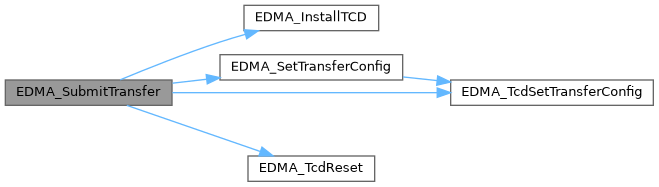

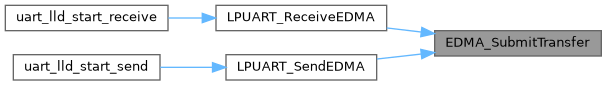

◆ EDMA_SubmitTransfer()

| status_t EDMA_SubmitTransfer | ( | edma_handle_t * | handle, |

| const edma_transfer_config_t * | config | ||

| ) |

Submits the eDMA transfer request.

This function submits the eDMA transfer request according to the transfer configuration structure. In scatter gather mode, call this function will add a configured tcd to the circular list of tcd pool. The tcd pools is setup by call function EDMA_InstallTCDMemory before.

- Parameters

-

handle eDMA handle pointer. config Pointer to eDMA transfer configuration structure.

- Return values

-

kStatus_EDMA_Success It means submit transfer request succeed. kStatus_EDMA_QueueFull It means TCD queue is full. Submit transfer request is not allowed. kStatus_EDMA_Busy It means the given channel is busy, need to submit request later.

brief Submits the eDMA transfer request.

This function submits the eDMA transfer request according to the transfer configuration structure. In scatter gather mode, call this function will add a configured tcd to the circular list of tcd pool. The tcd pools is setup by call function EDMA_InstallTCDMemory before.

param handle eDMA handle pointer. param config Pointer to eDMA transfer configuration structure. retval kStatus_EDMA_Success It means submit transfer request succeed. retval kStatus_EDMA_QueueFull It means TCD queue is full. Submit transfer request is not allowed. retval kStatus_EDMA_Busy It means the given channel is busy, need to submit request later.

Definition at line 956 of file fsl_edma.c.

Referenced by LPUART_ReceiveEDMA(), and LPUART_SendEDMA().

◆ EDMA_TcdDisableInterrupts()

| void EDMA_TcdDisableInterrupts | ( | edma_tcd_t * | tcd, |

| uint32_t | mask | ||

| ) |

Disables the interrupt source for the eDMA TCD.

- Parameters

-

tcd Point to the TCD structure. mask The mask of interrupt source to be set. Users need to use the defined edma_interrupt_enable_t type.

brief Disables the interrupt source for the eDMA TCD.

param tcd Point to the TCD structure. param mask The mask of interrupt source to be set. Users need to use the defined edma_interrupt_enable_t type.

Definition at line 610 of file fsl_edma.c.

◆ EDMA_TcdEnableAutoStopRequest()

|

inlinestatic |

Sets the auto stop request for the eDMA TCD.

If enabling the auto stop request, the eDMA hardware automatically disables the hardware channel request.

- Parameters

-

tcd A pointer to the TCD structure. enable The command to enable (true) or disable (false).

Definition at line 614 of file fsl_edma.h.

◆ EDMA_TcdEnableInterrupts()

| void EDMA_TcdEnableInterrupts | ( | edma_tcd_t * | tcd, |

| uint32_t | mask | ||

| ) |

Enables the interrupt source for the eDMA TCD.

- Parameters

-

tcd Point to the TCD structure. mask The mask of interrupt source to be set. Users need to use the defined edma_interrupt_enable_t type.

brief Enables the interrupt source for the eDMA TCD.

param tcd Point to the TCD structure. param mask The mask of interrupt source to be set. Users need to use the defined edma_interrupt_enable_t type.

Definition at line 586 of file fsl_edma.c.

◆ EDMA_TcdReset()

| void EDMA_TcdReset | ( | edma_tcd_t * | tcd | ) |

Sets all fields to default values for the TCD structure.

This function sets all fields for this TCD structure to default value.

- Parameters

-

tcd Pointer to the TCD structure.

- Note

- This function enables the auto stop request feature.

brief Sets all fields to default values for the TCD structure.

This function sets all fields for this TCD structure to default value.

param tcd Pointer to the TCD structure. note This function enables the auto stop request feature.

Definition at line 392 of file fsl_edma.c.

Referenced by EDMA_ResetChannel(), EDMA_SubmitTransfer(), LPSPI_MasterTransferEDMA(), and LPSPI_SlaveTransferEDMA().

◆ EDMA_TcdSetBandWidth()

|

inlinestatic |

Sets the bandwidth for the eDMA TCD.

Because the eDMA processes the minor loop, it continuously generates read/write sequences until the minor count is exhausted. The bandwidth forces the eDMA to stall after the completion of each read/write access to control the bus request bandwidth seen by the crossbar switch.

- Parameters

-

tcd A pointer to the TCD structure. bandWidth A bandwidth setting, which can be one of the following: - kEDMABandwidthStallNone

- kEDMABandwidthStall4Cycle

- kEDMABandwidthStall8Cycle

Definition at line 585 of file fsl_edma.h.

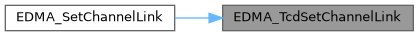

◆ EDMA_TcdSetChannelLink()

| void EDMA_TcdSetChannelLink | ( | edma_tcd_t * | tcd, |

| edma_channel_link_type_t | type, | ||

| uint32_t | linkedChannel | ||

| ) |

Sets the channel link for the eDMA TCD.

This function configures either a minor link or a major link. The minor link means the channel link is triggered every time CITER decreases by 1. The major link means that the channel link is triggered when the CITER is exhausted.

- Note

- Users should ensure that DONE flag is cleared before calling this interface, or the configuration is invalid.

- Parameters

-

tcd Point to the TCD structure. type Channel link type, it can be one of: - kEDMA_LinkNone

- kEDMA_MinorLink

- kEDMA_MajorLink

linkedChannel The linked channel number.

brief Sets the channel link for the eDMA TCD.

This function configures either a minor link or a major link. The minor link means the channel link is triggered every time CITER decreases by 1. The major link means that the channel link is triggered when the CITER is exhausted.

note Users should ensure that DONE flag is cleared before calling this interface, or the configuration is invalid. param tcd Point to the TCD structure. param type Channel link type, it can be one of: arg kEDMA_LinkNone arg kEDMA_MinorLink arg kEDMA_MajorLink param linkedChannel The linked channel number.

Definition at line 518 of file fsl_edma.c.

Referenced by EDMA_SetChannelLink().

◆ EDMA_TcdSetMinorOffsetConfig()

| void EDMA_TcdSetMinorOffsetConfig | ( | edma_tcd_t * | tcd, |

| const edma_minor_offset_config_t * | config | ||

| ) |

Configures the eDMA TCD minor offset feature.

A minor offset is a signed-extended value added to the source address or a destination address after each minor loop.

- Parameters

-

tcd A point to the TCD structure. config A pointer to the minor offset configuration structure.

brief Configures the eDMA TCD minor offset feature.

A minor offset is a signed-extended value added to the source address or a destination address after each minor loop.

param tcd A point to the TCD structure. param config A pointer to the minor offset configuration structure.

Definition at line 488 of file fsl_edma.c.

◆ EDMA_TcdSetModulo()

| void EDMA_TcdSetModulo | ( | edma_tcd_t * | tcd, |

| edma_modulo_t | srcModulo, | ||

| edma_modulo_t | destModulo | ||

| ) |

Sets the source modulo and the destination modulo for the eDMA TCD.

This function defines a specific address range specified to be the value after (SADDR + SOFF)/(DADDR + DOFF) calculation is performed or the original register value. It provides the ability to implement a circular data queue easily.

- Parameters

-

tcd A pointer to the TCD structure. srcModulo A source modulo value. destModulo A destination modulo value.

brief Sets the source modulo and the destination modulo for the eDMA TCD.

This function defines a specific address range specified to be the value after (SADDR + SOFF)/(DADDR + DOFF) calculation is performed or the original register value. It provides the ability to implement a circular data queue easily.

param tcd A pointer to the TCD structure. param srcModulo A source modulo value. param destModulo A destination modulo value.

Definition at line 568 of file fsl_edma.c.

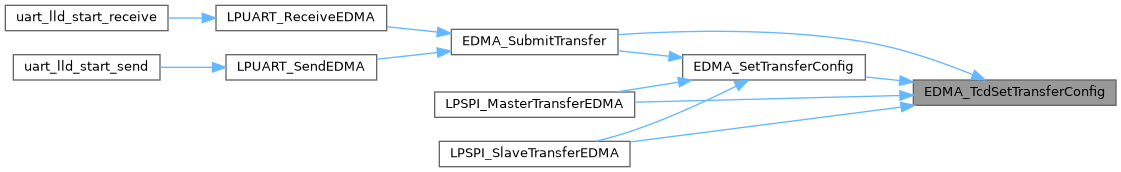

◆ EDMA_TcdSetTransferConfig()

| void EDMA_TcdSetTransferConfig | ( | edma_tcd_t * | tcd, |

| const edma_transfer_config_t * | config, | ||

| edma_tcd_t * | nextTcd | ||

| ) |

Configures the eDMA TCD transfer attribute.

The TCD is a transfer control descriptor. The content of the TCD is the same as the hardware TCD registers. The STCD is used in the scatter-gather mode. This function configures the TCD transfer attribute, including source address, destination address, transfer size, address offset, and so on. It also configures the scatter gather feature if the user supplies the next TCD address. Example:

- Parameters

-

tcd Pointer to the TCD structure. config Pointer to eDMA transfer configuration structure. nextTcd Pointer to the next TCD structure. It can be NULL if users do not want to enable scatter/gather feature.

- Note

- TCD address should be 32 bytes aligned or it causes an eDMA error.

- If the nextTcd is not NULL, the scatter gather feature is enabled and DREQ bit is cleared in the previous transfer configuration, which is set in the EDMA_TcdReset.

brief Configures the eDMA TCD transfer attribute.

The TCD is a transfer control descriptor. The content of the TCD is the same as the hardware TCD registers. The STCD is used in the scatter-gather mode. This function configures the TCD transfer attribute, including source address, destination address, transfer size, address offset, and so on. It also configures the scatter gather feature if the user supplies the next TCD address. Example: code edma_transfer_t config = { ... } edma_tcd_t tcd __aligned(32); edma_tcd_t nextTcd __aligned(32); EDMA_TcdSetTransferConfig(&tcd, &config, &nextTcd); endcode

param tcd Pointer to the TCD structure. param config Pointer to eDMA transfer configuration structure. param nextTcd Pointer to the next TCD structure. It can be NULL if users do not want to enable scatter/gather feature. note TCD address should be 32 bytes aligned or it causes an eDMA error. note If the nextTcd is not NULL, the scatter gather feature is enabled and DREQ bit is cleared in the previous transfer configuration, which is set in the EDMA_TcdReset.

Definition at line 439 of file fsl_edma.c.

Referenced by EDMA_SetTransferConfig(), EDMA_SubmitTransfer(), LPSPI_MasterTransferEDMA(), and LPSPI_SlaveTransferEDMA().

◆ EDMA_TriggerChannelStart()

|

inlinestatic |

Starts the eDMA transfer by using the software trigger.

This function starts a minor loop transfer.

- Parameters

-

base eDMA peripheral base address. channel eDMA channel number.

Definition at line 684 of file fsl_edma.h.

Variable Documentation

◆ ATTR

| __IO uint16_t _edma_tcd::ATTR |

ATTR register, source/destination transfer size and modulo

Definition at line 210 of file fsl_edma.h.

Referenced by EDMA_CreateHandle(), EDMA_InstallTCD(), EDMA_TcdReset(), EDMA_TcdSetModulo(), and EDMA_TcdSetTransferConfig().

◆ base

| DMA_Type* _edma_handle::base |

eDMA peripheral base address.

Definition at line 249 of file fsl_edma.h.

Referenced by EDMA_AbortTransfer(), EDMA_CreateHandle(), EDMA_GetNextTCDAddress(), EDMA_HandleIRQ(), EDMA_StartTransfer(), EDMA_StopTransfer(), EDMA_SubmitTransfer(), LPSPI_MasterTransferEDMA(), LPSPI_MasterTransferGetCountEDMA(), LPSPI_SlaveTransferEDMA(), LPSPI_SlaveTransferGetCountEDMA(), LPUART_TransferGetReceiveCountEDMA(), and LPUART_TransferGetSendCountEDMA().

◆ BITER

| __IO uint16_t _edma_tcd::BITER |

BITER register, begin minor loop count.

Definition at line 218 of file fsl_edma.h.

Referenced by EDMA_CreateHandle(), EDMA_InstallTCD(), EDMA_TcdReset(), EDMA_TcdSetChannelLink(), and EDMA_TcdSetTransferConfig().

◆ callback

| edma_callback _edma_handle::callback |

Callback function for major count exhausted.

Definition at line 247 of file fsl_edma.h.

Referenced by EDMA_HandleIRQ(), and EDMA_SetCallback().

◆ channel

| uint8_t _edma_handle::channel |

eDMA channel number.

Definition at line 251 of file fsl_edma.h.

Referenced by EDMA_AbortTransfer(), EDMA_CreateHandle(), EDMA_GetNextTCDAddress(), EDMA_HandleIRQ(), EDMA_StartTransfer(), EDMA_StopTransfer(), EDMA_SubmitTransfer(), LPSPI_MasterTransferEDMA(), LPSPI_MasterTransferGetCountEDMA(), LPSPI_SlaveTransferEDMA(), LPSPI_SlaveTransferGetCountEDMA(), LPUART_TransferGetReceiveCountEDMA(), and LPUART_TransferGetSendCountEDMA().

◆ channelPriority

| uint8_t _edma_channel_Preemption_config::channelPriority |

Channel priority

Definition at line 189 of file fsl_edma.h.

◆ CITER

| __IO uint16_t _edma_tcd::CITER |

CITER register, current minor loop numbers, for unfinished minor loop.

Definition at line 215 of file fsl_edma.h.

Referenced by EDMA_CreateHandle(), EDMA_InstallTCD(), EDMA_TcdReset(), EDMA_TcdSetChannelLink(), and EDMA_TcdSetTransferConfig().

◆ CSR

| __IO uint16_t _edma_tcd::CSR |

CSR register, for TCD control status

Definition at line 217 of file fsl_edma.h.

Referenced by EDMA_CreateHandle(), EDMA_InstallTCD(), EDMA_StartTransfer(), EDMA_SubmitTransfer(), EDMA_TcdDisableInterrupts(), EDMA_TcdEnableAutoStopRequest(), EDMA_TcdEnableInterrupts(), EDMA_TcdReset(), EDMA_TcdSetBandWidth(), EDMA_TcdSetChannelLink(), and EDMA_TcdSetTransferConfig().

◆ DADDR

| __IO uint32_t _edma_tcd::DADDR |

DADDR register, used for destination address

Definition at line 213 of file fsl_edma.h.

Referenced by EDMA_CreateHandle(), EDMA_InstallTCD(), EDMA_TcdReset(), and EDMA_TcdSetTransferConfig().

◆ destAddr

| uint32_t _edma_transfer_config::destAddr |

Destination data address.

Definition at line 173 of file fsl_edma.h.

Referenced by LPSPI_MasterTransferEDMA(), and LPSPI_SlaveTransferEDMA().

◆ destOffset

| int16_t _edma_transfer_config::destOffset |

Sign-extended offset applied to the current destination address to form the next-state value as each destination write is completed.

Definition at line 178 of file fsl_edma.h.

Referenced by LPSPI_MasterTransferEDMA(), and LPSPI_SlaveTransferEDMA().

◆ destTransferSize

| edma_transfer_size_t _edma_transfer_config::destTransferSize |

Destination data transfer size.

Definition at line 175 of file fsl_edma.h.

Referenced by LPSPI_MasterTransferEDMA(), and LPSPI_SlaveTransferEDMA().

◆ DLAST_SGA

| __IO uint32_t _edma_tcd::DLAST_SGA |

DLASTSGA register, next tcd address used in scatter-gather mode

Definition at line 216 of file fsl_edma.h.

Referenced by EDMA_CreateHandle(), EDMA_InstallTCD(), EDMA_StartTransfer(), EDMA_SubmitTransfer(), EDMA_TcdReset(), and EDMA_TcdSetTransferConfig().

◆ DOFF

| __IO uint16_t _edma_tcd::DOFF |

DOFF register, used for destination offset

Definition at line 214 of file fsl_edma.h.

Referenced by EDMA_CreateHandle(), EDMA_InstallTCD(), EDMA_TcdReset(), and EDMA_TcdSetTransferConfig().

◆ enableChannelPreemption

| bool _edma_channel_Preemption_config::enableChannelPreemption |

If true: a channel can be suspended by other channel with higher priority

Definition at line 187 of file fsl_edma.h.

◆ enableContinuousLinkMode

| bool _edma_config::enableContinuousLinkMode |

Enable (true) continuous link mode. Upon minor loop completion, the channel activates again if that channel has a minor loop channel link enabled and the link channel is itself.

Definition at line 154 of file fsl_edma.h.

◆ enableDebugMode

| bool _edma_config::enableDebugMode |

Enable(true) eDMA debug mode. When in debug mode, the eDMA stalls the start of a new channel. Executing channels are allowed to complete.

Definition at line 161 of file fsl_edma.h.

◆ enableDestMinorOffset

| bool _edma_minor_offset_config::enableDestMinorOffset |

Enable(true) or Disable(false) destination minor loop offset.

Definition at line 196 of file fsl_edma.h.

◆ enableHaltOnError

| bool _edma_config::enableHaltOnError |

Enable (true) transfer halt on error. Any error causes the HALT bit to set. Subsequently, all service requests are ignored until the HALT bit is cleared.

Definition at line 157 of file fsl_edma.h.

Referenced by dmaInit().

◆ enablePreemptAbility

| bool _edma_channel_Preemption_config::enablePreemptAbility |

If true: a channel can suspend other channel with low priority

Definition at line 188 of file fsl_edma.h.

◆ enableRoundRobinArbitration

| bool _edma_config::enableRoundRobinArbitration |

Enable (true) round robin channel arbitration method or fixed priority arbitration is used for channel selection

Definition at line 159 of file fsl_edma.h.

◆ enableSrcMinorOffset

| bool _edma_minor_offset_config::enableSrcMinorOffset |

Enable(true) or Disable(false) source minor loop offset.

Definition at line 195 of file fsl_edma.h.

◆ flags

| uint8_t _edma_handle::flags |

The status of the current channel.

Definition at line 257 of file fsl_edma.h.

Referenced by EDMA_InstallTCDMemory(), EDMA_StartTransfer(), EDMA_StopTransfer(), and EDMA_SubmitTransfer().

◆ header

| volatile int8_t _edma_handle::header |

The first TCD index. Should point to the next TCD to be loaded into the eDMA engine.

Definition at line 252 of file fsl_edma.h.

Referenced by EDMA_AbortTransfer(), EDMA_HandleIRQ(), and EDMA_InstallTCDMemory().

◆ majorLoopCounts

| uint32_t _edma_transfer_config::majorLoopCounts |

Major loop iteration count.

Definition at line 181 of file fsl_edma.h.

Referenced by LPSPI_MasterTransferEDMA(), and LPSPI_SlaveTransferEDMA().

◆ minorLoopBytes

| uint32_t _edma_transfer_config::minorLoopBytes |

Bytes to transfer in a minor loop

Definition at line 180 of file fsl_edma.h.

Referenced by LPSPI_MasterTransferEDMA(), and LPSPI_SlaveTransferEDMA().

◆ minorOffset

| uint32_t _edma_minor_offset_config::minorOffset |

Offset for a minor loop mapping.

Definition at line 197 of file fsl_edma.h.

◆ NBYTES

| __IO uint32_t _edma_tcd::NBYTES |

Nbytes register, minor loop length in bytes

Definition at line 211 of file fsl_edma.h.

Referenced by EDMA_CreateHandle(), EDMA_InstallTCD(), EDMA_TcdReset(), EDMA_TcdSetMinorOffsetConfig(), and EDMA_TcdSetTransferConfig().

◆ SADDR

| __IO uint32_t _edma_tcd::SADDR |

SADDR register, used to save source address

Definition at line 208 of file fsl_edma.h.

Referenced by EDMA_CreateHandle(), EDMA_InstallTCD(), EDMA_TcdReset(), and EDMA_TcdSetTransferConfig().

◆ SLAST

| __IO uint32_t _edma_tcd::SLAST |

SLAST register

Definition at line 212 of file fsl_edma.h.

Referenced by EDMA_CreateHandle(), EDMA_InstallTCD(), and EDMA_TcdReset().

◆ SOFF

| __IO uint16_t _edma_tcd::SOFF |

SOFF register, save offset bytes every transfer

Definition at line 209 of file fsl_edma.h.

Referenced by EDMA_CreateHandle(), EDMA_InstallTCD(), EDMA_TcdReset(), and EDMA_TcdSetTransferConfig().

◆ srcAddr

| uint32_t _edma_transfer_config::srcAddr |

Source data address.

Definition at line 172 of file fsl_edma.h.

Referenced by LPSPI_MasterTransferEDMA(), and LPSPI_SlaveTransferEDMA().

◆ srcOffset

| int16_t _edma_transfer_config::srcOffset |

Sign-extended offset applied to the current source address to form the next-state value as each source read is completed.

Definition at line 176 of file fsl_edma.h.

Referenced by LPSPI_MasterTransferEDMA(), and LPSPI_SlaveTransferEDMA().

◆ srcTransferSize

| edma_transfer_size_t _edma_transfer_config::srcTransferSize |

Source data transfer size.

Definition at line 174 of file fsl_edma.h.

Referenced by LPSPI_MasterTransferEDMA(), and LPSPI_SlaveTransferEDMA().

◆ tail

| volatile int8_t _edma_handle::tail |

The last TCD index. Should point to the next TCD to be stored into the memory pool.

Definition at line 253 of file fsl_edma.h.

Referenced by EDMA_AbortTransfer(), EDMA_InstallTCDMemory(), and EDMA_SubmitTransfer().

◆ tcdPool

| edma_tcd_t* _edma_handle::tcdPool |

Pointer to memory stored TCDs.

Definition at line 250 of file fsl_edma.h.

Referenced by EDMA_AbortTransfer(), EDMA_HandleIRQ(), EDMA_InstallTCDMemory(), EDMA_StartTransfer(), and EDMA_SubmitTransfer().

◆ tcdSize

| volatile int8_t _edma_handle::tcdSize |

The total number of TCD slots in the queue.

Definition at line 256 of file fsl_edma.h.

Referenced by EDMA_GetUnusedTCDNumber(), EDMA_HandleIRQ(), EDMA_InstallTCDMemory(), and EDMA_SubmitTransfer().

◆ tcdUsed

| volatile int8_t _edma_handle::tcdUsed |

The number of used TCD slots. Should reflect the number of TCDs can be used/loaded in the memory.

Definition at line 254 of file fsl_edma.h.

Referenced by EDMA_AbortTransfer(), EDMA_GetUnusedTCDNumber(), EDMA_HandleIRQ(), EDMA_InstallTCDMemory(), and EDMA_SubmitTransfer().

◆ userData

| void* _edma_handle::userData |

Callback function parameter.

Definition at line 248 of file fsl_edma.h.

Referenced by EDMA_HandleIRQ(), and EDMA_SetCallback().