Functions | |

| Gpio | getCommsLedPin () |

| Gpio | getRunningLedPin () |

| Gpio | getWarningLedPin () |

| static void | setSerialConfigurationOverrides () |

| static void | subaru_eg33_boardDefaultConfiguration () |

| Board-specific configuration defaults. | |

| static void | subaru_eg33_boardConfigOverrides () |

| static void | board_init_ext_gpios () |

| void | boardInit () |

| Board-specific initialization code. | |

| void | setup_custom_board_overrides () |

Variables | |

| static const struct mc33810_config | mc33810_odd |

| static const struct mc33810_config | mc33810_even |

Function Documentation

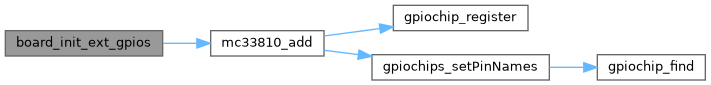

◆ board_init_ext_gpios()

|

static |

Definition at line 348 of file board_configuration.cpp.

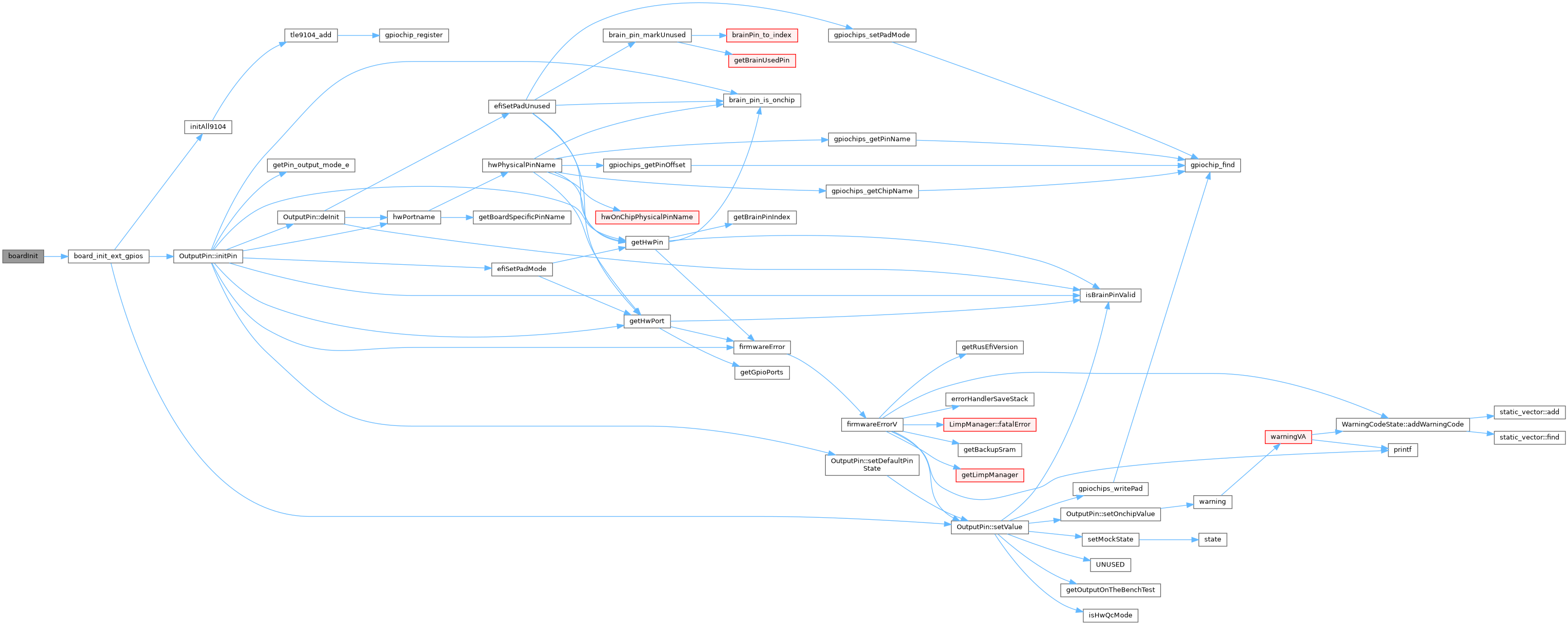

◆ boardInit()

| void boardInit | ( | void | ) |

Board-specific initialization code.

Definition at line 367 of file board_configuration.cpp.

◆ getCommsLedPin()

| Gpio getCommsLedPin | ( | ) |

See https://rusefi.com/s/super-uaefi

See https://rusefi.com/s/uaefi121

Definition at line 16 of file board_configuration.cpp.

◆ getRunningLedPin()

| Gpio getRunningLedPin | ( | ) |

Definition at line 20 of file board_configuration.cpp.

◆ getWarningLedPin()

| Gpio getWarningLedPin | ( | ) |

Definition at line 24 of file board_configuration.cpp.

◆ setSerialConfigurationOverrides()

|

static |

Definition at line 29 of file board_configuration.cpp.

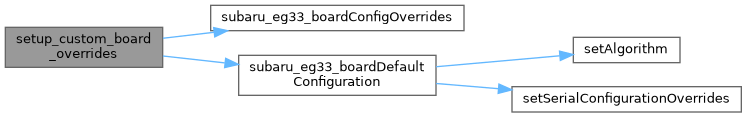

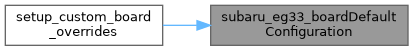

◆ setup_custom_board_overrides()

| void setup_custom_board_overrides | ( | ) |

Definition at line 371 of file board_configuration.cpp.

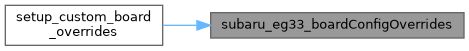

◆ subaru_eg33_boardConfigOverrides()

|

static |

Definition at line 218 of file board_configuration.cpp.

Referenced by setup_custom_board_overrides().

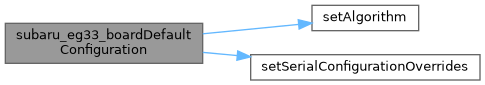

◆ subaru_eg33_boardDefaultConfiguration()

|

static |

Board-specific configuration defaults.

Definition at line 43 of file board_configuration.cpp.

Referenced by setup_custom_board_overrides().

Variable Documentation

◆ mc33810_even

|

static |

Definition at line 299 of file board_configuration.cpp.

Referenced by board_init_ext_gpios().

◆ mc33810_odd

|

static |

Definition at line 248 of file board_configuration.cpp.

Referenced by board_init_ext_gpios().